IR-drop

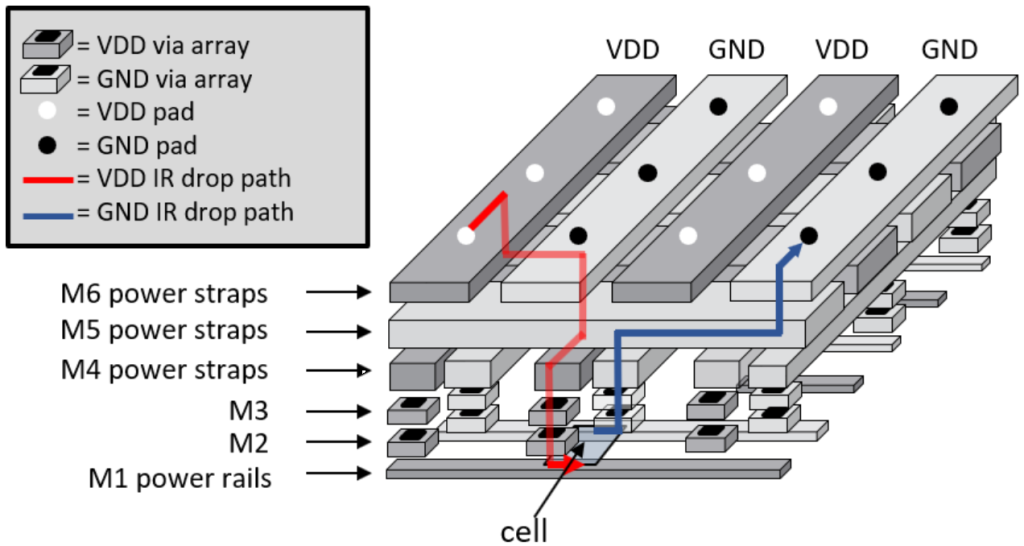

IR drop means the voltage drop that occurs to reach the Vdd pin of the standard cell in the metal wires that make up the power grid. If IR drop occur and the voltage supplied to the standard cell is reduced, the performance of the standard cell can be reduced, resulting in timing violations such as setup violations.

Conventional tool for analyzing IR drops computes IR drops by solving a large linear system of equations. But in the case of dynamic IR drops, the larger the circuit, the more time-consuming it becomes. In this work, we aim to study a model that uses machine learning techniques to quickly predict IR drop.

KEYWORDS IR drop

Related Publications Fast Prediction of Dynamic IR-Drop Using Recurrent U-Net Architecture

PDN Synthesis

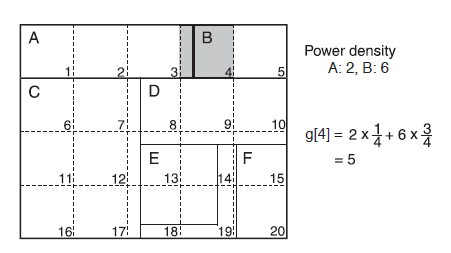

Power distribution network (PDN) is responsible for supplying the current from power pads to standard cells, while the constraint on IR-drop is respected.

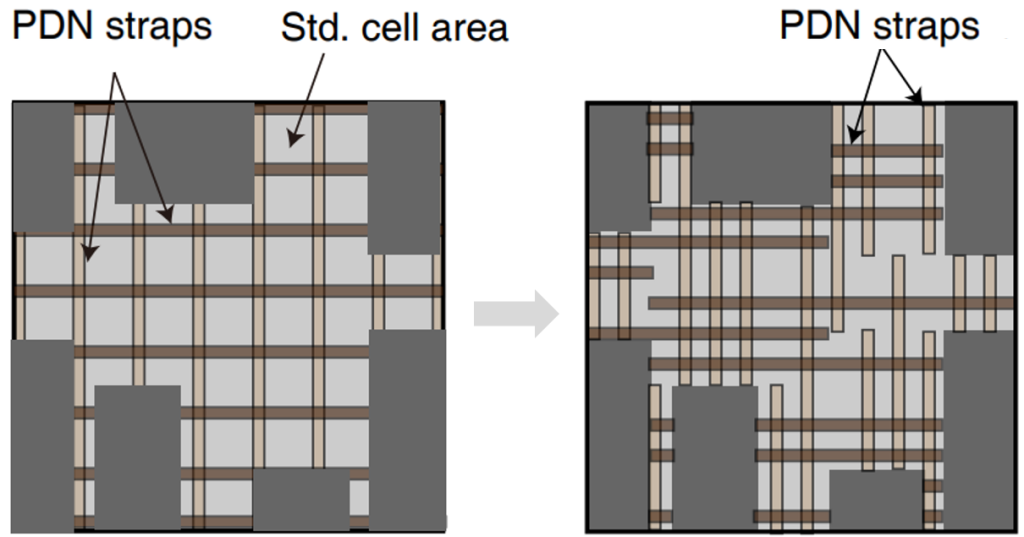

Conventional PDN synthesis method is to assume regular PDN before cell placement is performed. With technology scaling, PDN requires more routing resources but wire resistance increases. We aim to study how to insert minimum number of power straps in irregular way using machine learning.

KEYWORDS PDN, Inserting power strap

Related Publications Integrated Power Distribution Network Synthesis for Mixed Macro Blocks and Standard Cells

3D IC Floor-planning

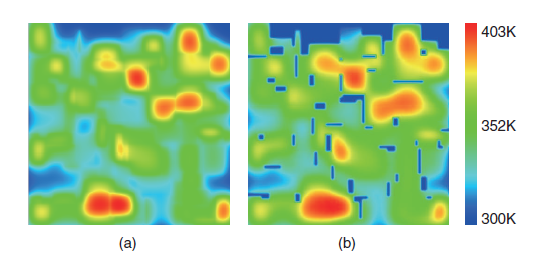

Three-dimensional integrated circuits (3D IC) made up of an IC stack provide higher devise density and higher bandwidth. Also, it may accommodate multiple different functioning modules at different process nodes. However, the thermal issue is a critical challenge in 3D IC. Vertically stacked multiple layers cause a rapid increase in power density and lower thermal conductivity.

Therefore, thermal-aware 3D IC floor-planning is important. Our goal is to automatically optimize the chip temperature with other objectives like chip area, wirelength. Also, optimizing floorplan should be faster than simulation-based model still with high accuracy.

KEYWORDS Thermal-aware 3D IC floor-planning

Related Publications Thermal Signature- A Simple Yet Accurate Thermal Index for Floorplan Optimization

CTS

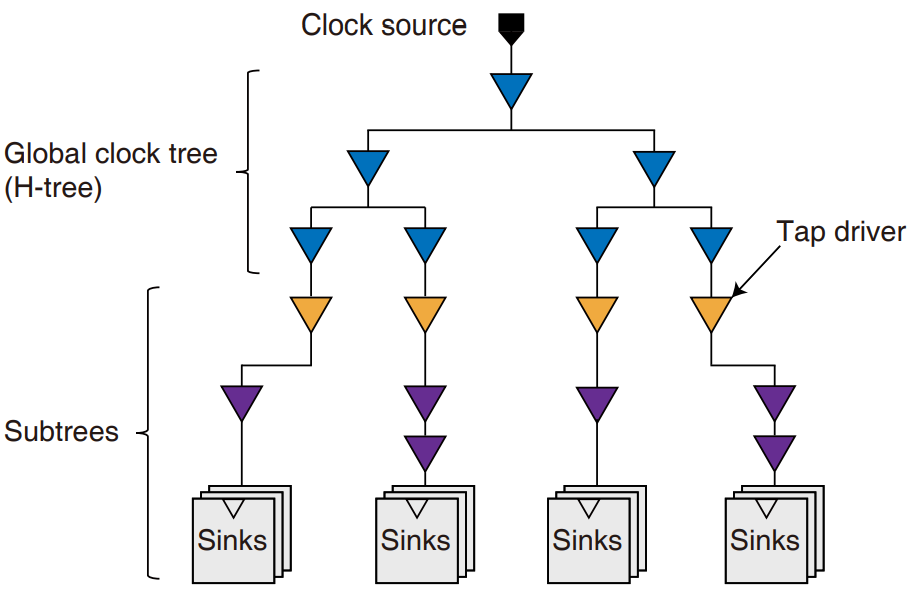

Clock tree synthesis is to balance the delays of clock paths by creating a buffer/inverter clock network. The essence is to achieve timing convergence by reducing the delay differences on each clock path.

Methods like multisource clock tree synthesis (MSCTS), which is used to maximize common clock path, so that on-chip variation (OCV) clock skew is minimized. Tap drivers with large driving strength are located in a layout, while they are connected to clock source through balanced tree. Each tap driver then becomes a clock source of a local clock tree.

KEYWORDS MSCTS

Related Publications Multisource clock tree synthesis through sink clustering and fast clock latency prediction

Analog Layout Automation

Analog integrated circuits (ICs) play an important role in many system-on-chip (SoC) design applications, such as consumer electronics, bioelectronics, automotive electronics, internet of things (IoT). But electronic design automation for the analog IC, especially analog layout design has been a manual, time consuming. We use machine learning to reduce design time in this process.

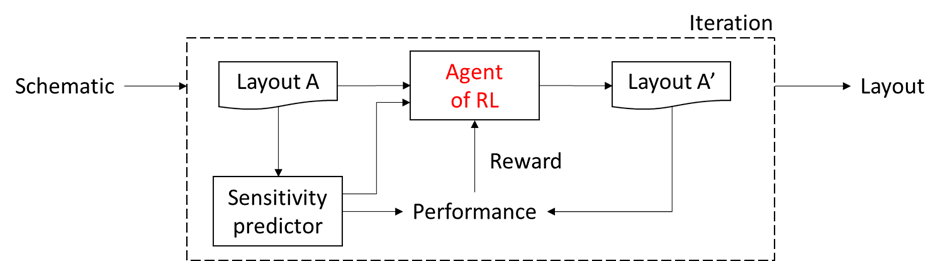

To get a desired specification of layout, designers have to do placement, routing and SPICE simulation many times. We propose a reinforcement learning that can replace the designer’s repetition. Agent receives layout and sensitivity and is trained by performance as a reward. After training, agent modifies layout for target specification.

KEYWORDS Agent of RL(reinforcement learning)

Related Publications Block-level power net routing of analog circuit using reinforcement learning