Logic Synthesis

The existing computing system follows the Von Neumann architecture that the CPU is responsible for control and arithmetic/logic operation, and memory is used simply to store and load data. The performance gap between two separated devices increases more due to scaling down, and it becomes major performance issue called Von Neumann botteneck. Processing-in memory (PIM) is proposed to solve this problem. PIM performs CPU operation in memory without data transferring between CPU and memory via system bus.

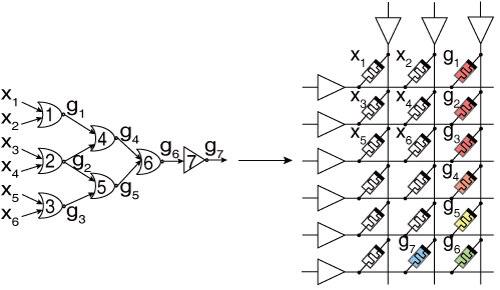

A memristive memory allows logic functions to be realized as a sequence of NOR, IMP, or MAJ operations. We propose an efficient netlist rewriting method to extract an NOR-INV graph (NIG), IMP-INV graph (IIG), or MAJ-INV graph (MIG) with minimum latency or smallest area. The final NIG, IIG, or MIG is mapped on actual memristive memory array; a mapping algorithm is studied for an optimal array.

Memory Compiler

Modern state-of-the-art memory are highly important component embedded in System-on-Chip (SoC). Different applications require different architectures and sizes of memories. But, manual design is too hard and time consuming. This hard work is solved by a memory compiler that software tool could automatically generate memories of different architectures and configurations based on user-defined parameters.

In this work, we aim to study that PIM memory compiler is a tool that synthesize not only memory array but peripheral circuits such as buffer, DAC, and MUX to meet configuration.