Chong-Min Kyung Sungjoo Yoo *Editors*

# Energy-Aware System Design

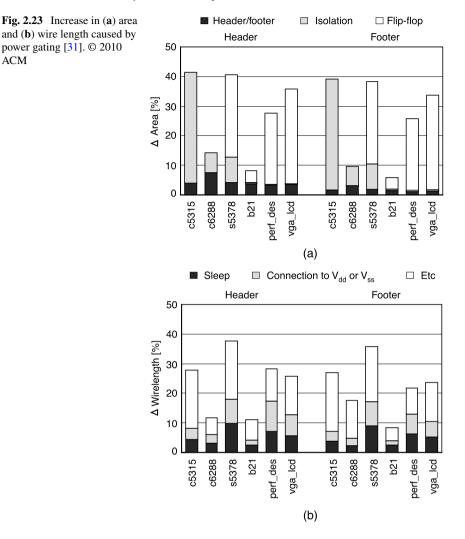

Algorithms and Architectures

Energy-Aware System Design

Chong-Min Kyung • Sungjoo Yoo Editors

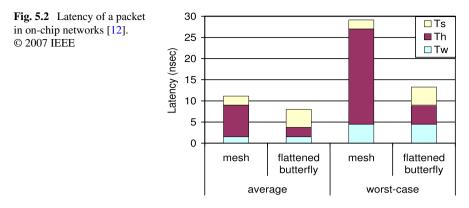

# Energy-Aware System Design

Algorithms and Architectures

*Editors* Prof. Chong-Min Kyung Electrical Engineering KAIST Gwahak-ro 335, Yuseong-gu 305-701, Daejeon Republic of Korea kyung@ee.kaist.ac.kr

Prof. Sungjoo Yoo Embedded System Architecture Lab Electronic and Electrical Engineering POSTECH Hyoja-dong 31, Namgu 790-784, Pohang Republic of Korea sungjoo.yoo@postech.ac.kr

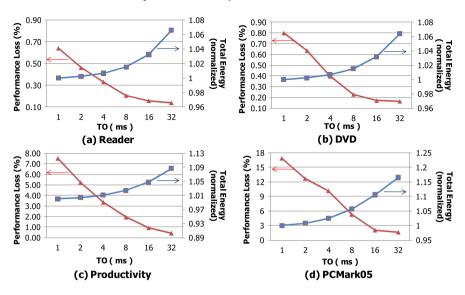

ISBN 978-94-007-1678-0 e-ISB DOI 10.1007/978-94-007-1679-7 Springer Dordrecht Heidelberg London New York

e-ISBN 978-94-007-1679-7

Library of Congress Control Number: 2011931517

© Springer Science+Business Media B.V. 2011

No part of this work may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, microfilming, recording or otherwise, without written permission from the Publisher, with the exception of any material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work.

Cover design: VTeX UAB, Lithuania

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

# Preface

Up to now the driving force of the development of most information technology (IT) devices and systems has mainly been performance-cost ratio boosting, but this has already begun to change. For some time energy consumption will occupy a growing portion in the design objective function of a large number of IT devices, especially in mobile, health, and ubiquitous applications. Using even the most energy-wise frugal technology, the energy we are spending for logic switching is still at least six orders of magnitude larger than the theoretical limit. The task of reducing that energy gap is not an easy one, but it can be quite effectively carried out if accompanied by a nicely coordinated effort of energy reduction among various design stages in the design process and among various components in the system.

A number of books have already been published that focus on low-energy design in one aspect, i.e., limited to an individual functional block such as on-chip networks, algorithms, processing cores, etc. Instead of merely enumerating various energy-reducing technologies, architectures, and algorithms, this book tries to explain the concepts of the most important functional blocks in typical information processing devices, e.g., memory blocks and systems, on-chip networks, and energy sources, such as batteries and fuel cells.

The most important market for low-energy devices, after the current booming smart phone, is probably energy-aware smart sensors. The variety of applications in the market is truly huge and expanding every year. With more and more traffic (both people and data) on the move, the planet is becoming more dangerous, as well as more exciting. The demand for installing smart sensors on various locations in our society as well as our bodies, i.e., on/in/outside the human body, obviously will grow. The scale and variety of threats against our society and each individual has never been so overwhelming, and this will probably escalate unless we carry out a systematic and coordinated effort toward building a safe society. We believe that the energy-aware smart sensor is one such attempt.

This book tries to show how the design of each functional block and algorithm can be changed by an addition of a new component: energy. Besides explanations of each functional block in early chapters, three application examples are given at the end: data/file storage systems, an artificial cochlea and retina, and a batteryoperated surveillance camera. We understand that the coverage is far from complete in terms of the variety of functional blocks, algorithms, and applications. Despite these imperfections, we sincerely hope, through this book, that the readers will gain some perspective and insights into energy-aware IT system design, which will lead us all toward a better, i.e., cleaner and safer society.

Daejeon, Republic of Korea Pohang, Republic of Korea Chong-Min Kyung Sungjoo Yoo

# Contents

| 1  | Introduction       1         Chong-Min Kyung and Sungjoo Yoo       1                                              |

|----|-------------------------------------------------------------------------------------------------------------------|

| 2  | Low-Power Circuits: A System-Level Perspective                                                                    |

| 3  | <b>Energy Awareness in Processor/Multi-Processor Design</b> 47<br>Jungsoo Kim, Sungjoo Yoo, and Chong-Min Kyung   |

| 4  | <b>Energy Awareness in Contemporary Memory Systems</b> 71<br>Jung Ho Ahn, Sungwoo Choo, and Seongil O             |

| 5  | <b>Energy-Aware On-Chip Networks</b>                                                                              |

| 6  | <b>Energy Awareness in Video Codec Design</b>                                                                     |

| 7  | Energy Generation and Conversion for Portable       Electronic Systems       149         Naehyuck Chang       149 |

| 8  | <b>3-D ICs for Low Power/Energy</b>                                                                               |

| 9  | Low Power Mobile Storage: SSD Case Study                                                                          |

| 10 | <b>Energy-Aware Surveillance Camera</b>                                                                           |

| 11 | Low Power Design Challenge in Biomedical<br>Implantable Electronics                                               |

# Contributors

Jung Ho Ahn Seoul National University, Seoul, Republic of Korea, gajh@snu.ac.kr

Naehyuck Chang Seoul National University, Seoul, Republic of Korea, naehyuck@elpl.snu.ac.kr

Sungwoo Choo Seoul National University, Seoul, Republic of Korea, choos@snu.ac.kr

Kyungsu Kang KAIST, Daejeon, Republic of Korea, kyungsu.kang@gmail.com

Giwon Kim KAIST, Daejeon, Republic of Korea, gwkim@vslab.kaist.ac.kr

Jaemoon Kim Samsung Electronics, Seoul, Republic of Korea, jaemoon.kim@gmail.com

John Kim KAIST, Daejeon, Republic of Korea, jjk12@kaist.edu

Jungsoo Kim KAIST, Daejeon, Republic of Korea, jungsoo.kim83@gmail.com

**Sung June Kim** Seoul National University, Seoul, Republic of Korea, kimsj@snu.ac.kr

Chong-Min Kyung KAIST, Daejeon, Republic of Korea, kyung@ee.kaist.ac.kr

Sangkwon Na Samsung Electronics, Seoul, Republic of Korea, sangkwon.na@gmail.com

Seongil O Seoul National University, Seoul, Republic of Korea, swdfish@snu.ac.kr

Chanik Park Samsung Electronics, Hwasung-City, Republic of Korea, ci.park@samsung.com

Youngsoo Shin KAIST, Daejeon, Republic of Korea, youngsoo@ee.kaist.ac.kr

Sungjoo Yoo POSTECH, Pohang, Republic of Korea, sungjoo.yoo@postech.ac.kr

# Chapter 1 Introduction

**Chong-Min Kyung and Sungjoo Yoo**

**Abstract** Energy efficiency is now an important keyword in everyday life, involving, e.g., CO<sub>2</sub> emissions, rising oil prices, longer battery lifetimes for smart phones, and lifelong functioning medical implants. This book addresses energy-efficient IT systems design, especially low power embedded systems design. This chapter discusses how a power-efficient design can be achieved by exploiting various slacks. For instance, temporal slack is utilized for dynamic voltage scaling while thermal slack is exploited for low-leakage operation, both methods thereby enabling low power consumption. This chapter also provides short introductions to the remaining chapters, which address aspects of low power embedded systems design such as low power circuits, memory, on-chip networks, power delivery, and low power design case studies of video surveillance systems, embedded storage, and medical implants.

# **1.1 Energy Awareness**

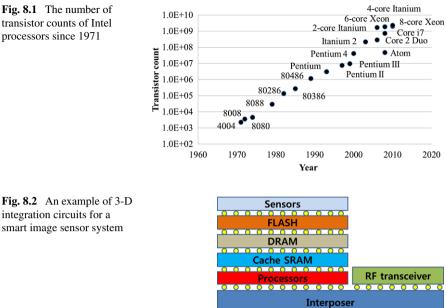

Power consumption has become the most important design goal in a wide range of electronic systems. There are two driving forces toward this trend: continuing device scaling and ever-increasing demand for higher computing power. First, device scaling continues to satisfy Moore's law via a conventional way of scaling (More Moore) and a new way of exploiting vertical integration (More than Moore) [1]. Second, mobile and IT convergence requires more computing power on the silicon chip than ever. Cell phones are now evolving to become mobile PCs. PCs and data centers are becoming commodities in the home and a must in industry. Both the supply enabled by device scaling and the demand triggered by the convergence trend realize more computation on chip (via multi-cores, integration of diverse functionalities

KAIST, Daejeon, Republic of Korea e-mail: kyung@ee.kaist.ac.kr

S. Yoo POSTECH, Pohang, Republic of Korea e-mail: sungjoo.yoo@postech.ac.kr

C.-M. Kyung (⊠)

Fig. 1.2 Battery capacity vs. computational demand [7]. © 2004 IEEE

on mobile SoCs, etc.) and finally more power consumption, incurring power-related issues and constraints.

We take two examples, the data center and the mobile phone, in order to investigate the impact of the current trend of increasing power consumption. Recently, data centers are becoming a crucial infrastructure in industry and government as well as in everybody's Internet usage. In the United States alone, data centers consumed 61 billion kilowatt-hours (kWh) in 2006, which is 1.5% of the total U.S. electricity consumption and amounts to a total electricity cost of about \$4.5 billion. In 2011, it is expected to reach more than 100 billion kWh [2]. The demand for data centers is projected to increase at 10% compound annual growth rate (CAGR) in the next decade [3].

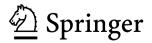

Figure 1.1 gives the decomposition of the data center operation cost [4]. It shows that about 34% (or more according to other sources) of the data center operation cost is power related. Power dissipation itself occupies 13%, power distribution and cooling 21%. Thus, reducing the power consumption and providing better cooling efficiency become critical in lowering the operation cost. Several approaches are being actively studied, including server rack level power management [5], capping the compute power in an I/O-intensive workload [6], and active liquid cooling [2].

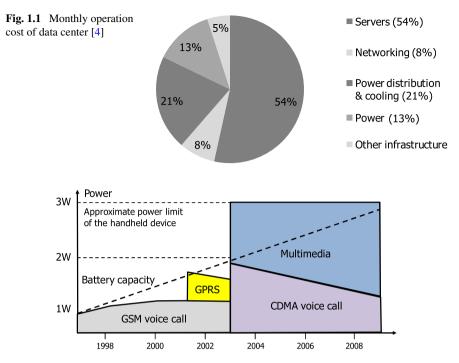

Figure 1.2 shows the trend of computing power requirement and battery capacity in the case of the cell phone [7]. The workload of the cell phone is decomposed into three parts: radio, multimedia, and application. Power consumption in the radio

#### 1 Introduction

is incurred by the power amplifier during conversation and the receiver in standby for paging. Power consumption of multimedia includes display, camera capture, video decoding/encoding, and three-dimensional (3D) graphics. Applications consume power in, e.g., Internet browsing, email, gaming, and photo handling. The workload of the cell phone increases by an order of magnitude every five years [8].

The battery in a smartphone is allocated only  $4-5 \text{ cm}^3$  and, thus, offers a maximum of about 2000 mAh as of 2010. However, as shown in Fig. 1.2, the battery capacity improves much more slowly than the increase in computational demand. Thus, battery-operated devices such as smartphones are limited by the energy density of the battery [9].

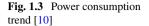

Figure 1.3 shows the power consumption trend as the technology node advances, where k represents the scaling factor, 1.4. The computing density is defined as the maximally possible number of computations per unit area and time. The figure shows that it increases at a rate of  $k^3$ . Also according to the figure, as scaling continues, leakage power increases much faster than active power. Note that the trend in Fig. 1.3 assumes that clock frequency continues to rise and voltage scaling slows down. If this trend, i.e., an explosion in power consumption, continues without solution, it will become a roadblock in the IT industry, which has benefited from the rapid increase in computing power during the past decades.

In reality, many low power design methods have been applied to avoid such an explosion in power consumption trend. However, since the power demand will continue to increase in the future, e.g., in cloud computing and smart IT devices (smartphone, smart TV, etc.), the trend itself will continue. The absolute quantity of power consumption continues to rise, even though the currently available low power design methods are applied. Thus, more innovations are required to further reduce power consumption.

Recently, power consumption has become limited by another constraint:  $CO_2$  emission. The constraint is general to everyday activities including computing. All personal, industrial, and governmental activities are now evaluated in terms of energy consumption or  $CO_2$  emission. Table 1.1 shows examples of energy efficiency measured in terms of number of Google searches [11]. One Google search consumes 1 kJ (0.0003 kWh) of energy on average, which translates into roughly 0.2 g of  $CO_2$ . As this example shows, energy awareness is expected to spread more widely in our everyday life as well as in the IT industry. The increasing amount of electricity usage of IT technology will result in more pressure to achieve green IT. Low power

| Activity                                                                      | Google searches | Energy consumption |

|-------------------------------------------------------------------------------|-----------------|--------------------|

| CO <sub>2</sub> emissions of an average daily newspaper (100% recycled paper) | 850             | 850 kJ             |

| A glass of orange juice                                                       | 1,050           | 1,050 kJ           |

| One load of dishes in an EnergyStar dishwasher                                | 5,100           | 5,100 kJ           |

| A five mile trip in the average U.S. automobile                               | 10,000          | 10,000 kJ          |

| A cheeseburger                                                                | 15,000          | 15,000 kJ          |

| Electricity consumed by the average U.S. household in one month               | 3,100,000       | 3,100,000 kJ       |

**Table 1.1** Energy and  $CO_2$  emission in terms of number of Google searches [11]. © Google, Inc.

design methods, like those we will present in this book, will contribute to realizing the green IT.

# **1.2 Energy-Aware Design**

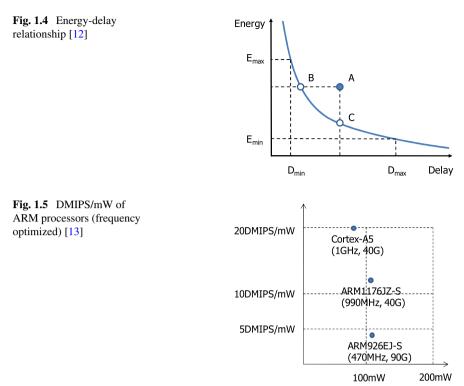

Energy-aware design, sometimes called energy-efficient design, is the design of a system to meet a given performance constraint with the minimum energy consumption. Figure 1.4 illustrates the relationship between energy and delay. At a given performance constraint, i.e., a delay constraint, an energy-efficient design is one having the minimum energy consumption satisfying the delay constraint. As the figure shows, such energy-efficient designs are called Pareto-optimal designs (e.g., points B and C in the figure) and form a front line (bold line in the figure) in the energy-delay relationship. Pareto-optimal points outperform other design candidates in terms of at least one design metric, e.g., energy or delay.

Energy-efficient design can be achieved in several ways at every level of abstraction, from system level down to transistor device level, as follows:

- System level: energy-aware algorithm (e.g., parallel data structure instead of sequential one), memory-aware software optimization (e.g., utilizing scratch pad memory)

- Architecture: multi-core (including parallel functional units), instruction set selection, dynamic voltage and frequency scaling, power gating

- Logic (or gate level): multi- $V_{\text{th}}/L_{\text{g}}/T_{\text{ox}}/V_{\text{dd}}$  designs (can also be considered in circuit level) instead of worst case design

- Circuit: device sizing, exploiting of transistor stacking to reduce leakage power, hybrid usage of dynamic and static circuit to meet the given delay constraint while minimizing power consumption, differential signaling to reduce voltage swing, etc.

- Device: high  $I_{\rm on}/I_{\rm off}$  devices, e.g., double-gate or back-gate transistors

Energy awareness means to consider an algorithm (i.e., function) and implementation in terms of a work/energy concept. Thus, energy efficiency is evaluated in terms

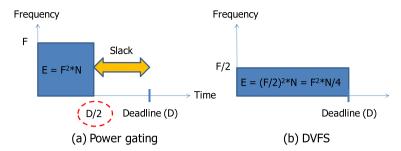

of the amount of work per energy and per unit time, e.g., DMIPS/mW. Figure 1.5 shows an architecture level example where the energy efficiency is improved from one processor generation to another. The figure shows three types of ARM processors, ARM926EJ-S (introduced in the early 2000s), ARM1176JZ-S (mid-2000s), and Cortex-A5 (2010). The figure shows that energy efficiency improves from one generation to the next while the total CPU power consumption remains at a similar level. The energy efficiency improvement results from two factors. One is technology. Note that the power number of ARM926EJ-S is from a 90 nm generic process, while the other two are from a 40 nm generic process. The other factor is architectural improvement. For instance, Cortex-A5 adopts SIMD operations while ARM926EJ-S does not.

Energy-efficient design aims at the best return on investment (ROI), i.e., maximum performance per energy spending. There are several low power design principles for obtaining the best ROI. One representative principle is matching computation and architecture. For instance, it is more energy efficient to run data parallel compute-intensive loops on the DSP instead of running them on the RISC processor. Another example is to utilize asymmetric and/or heterogeneous multi-cores to exploit the fact that single and multi-threaded applications coexist.

Many solutions have been presented at several abstraction levels for energyaware behavioral and architectural design. Most of the low power design techniques at higher levels than the transistor device level can be considered to exploit "slack" in various forms. In this book, we present several ideas utilizing slack. In the next subsection, we introduce several types of slack and explain how it is utilized for energy-efficient design.

# 1.3 Exploiting Slack Toward Energy-Aware Design

Slack is often called locality, which represents non-uniform, but not random characteristics. There are several types of slack: temporal, spatial, behavioral, architectural, process variation, thermal (2D and 3D), peak power slack, etc. We classify existing low power design methods depending on which type of slack they utilize as follows:

- 1. Temporal slack: power/clock gating and (conventional) dynamic voltage and frequency scaling, e.g., Intel SpeedStep

- 2. Spatial slack: multi-core, e.g., ARM Cortex-A9 MP

- 3. Behavior- and architecture-induced temporal slack: runtime distribution, e.g., Intel Data Center Manager

- 4. Process variation slack: adaptive voltage scaling, e.g., TI SmartReflex

- 5. Thermal slack: temperature-aware design, e.g., Intel Turbo Boost

- 6. Peak power slack: peak power-aware overclocking, e.g., Intel Turbo Boost

# 1.3.1 Temporal Slack

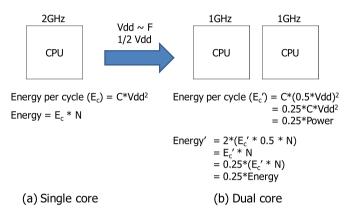

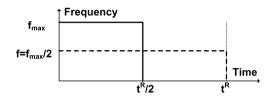

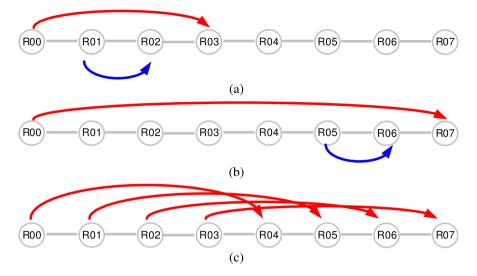

Figure 1.6 illustrates power gating and dynamic voltage and frequency scaling (DVFS). In Fig. 1.6(a), we assume that the processor has a workload of N clock cycles to be finished by the deadline, D. We also assume the quadratic relationship of switching energy/clock cycle  $\sim$  voltage<sup>2</sup> and a linear relationship between frequency and supply voltage, i.e., frequency  $\sim$  voltage. In Fig. 1.6(a), the processor runs at clock frequency F and the execution finishes at time D/2. Then, the processor sor enters an idle state during the slack by shutting off its power until time D. Since the power-gated processor consumes negligible power, the total switching energy consumption in this case is  $F^2N$ .

Figure 1.6(b) shows the case of applying DVFS to this example. If the workload of N clock cycles is known at time 0, the clock frequency can be set to F/2 just to meet the deadline, as shown in the figure. Thus, in this case, the new voltage becomes half the voltage in Fig. 1.6(a), and the energy consumption becomes 25% of that in Fig. 1.6(a), since new energy consumption ~ new\_voltage<sup>2</sup> ~ voltage<sup>2</sup>/4.

As shown in Fig. 1.6, DVFS exploits the slack in order to adjust the frequency and supply voltage such that they are just high enough to serve the current workload. For DVFS to be efficient, accurate workload estimation is critical. Many studies have been presented on workload estimation based on algorithm-specific information, compiler analysis [14], runtime prediction [15], etc. To meet the given deadline constraint, conventional DVFS methods utilize the worst case execution time

Fig. 1.6 Power gating vs. dynamic voltage and frequency scaling (DVFS)

Fig. 1.7 A benefit of multi-core: reduced energy consumption

(WCET) as the estimated workload and set the frequency to WCET/D. However, this method is pessimistic and loses opportunities for further energy reduction since there is a new slack which is the difference between the worst case and average case execution times. We will explain how to exploit this slack later in this section.

In reality, discrete voltage/frequency levels called operational points, e.g., the *P*-states in the Advanced Configuration and Power Interface (ACPI) [16], are usually applied in DVFS. Frequency change takes a variable latency depending on whether the required frequency is obtained by a simple clock division (a few clocks of latency) or by reconfiguring the PLL (typically, tens of microseconds).

#### 1.3.2 Spatial Slack Enabled by Newer Process Technology

In the past decade, the multi-core technology has proven to be effective in achieving better energy efficiency. One of the driving forces toward multi-core is that new process technology offers more room, i.e., more silicon area to accommodate more cores. Figure 1.7 shows how a multi-core processor improves energy efficiency. In Fig. 1.7(a), assume that a single processor executes a workload of N clock cycles at

2 GHz. In Fig. 1.7(b), assume that two processors are utilized and that each executes half the workload, N/2 clock cycles at 1 GHz.

Figure 1.7(b) shows that the switching energy consumption of each core in the dual-core processor is 25% of that in the single-core processor. Since each core executes half the workload, the total energy consumption of the dual-core is 25% of the single-core energy consumption, as shown in the figure.

In addition to spatial slack by new process technology, other factors affect multicore energy efficiency. On the positive side, the lower operating clock frequency (from 2 GHz to 1 GHz in Fig. 1.7) improves the per-core energy efficiency, e.g., by adopting shallower pipelines [12]. On the negative side, the first hurdle in achieving better energy efficiency is how to expose enough parallelism to fully utilize multiple cores. Another factor is that leakage power becomes more important, since leakage power is proportional to silicon die area (note that spatial slack means more silicon area usage) and the newer process technology incurs more leakage power consumption.

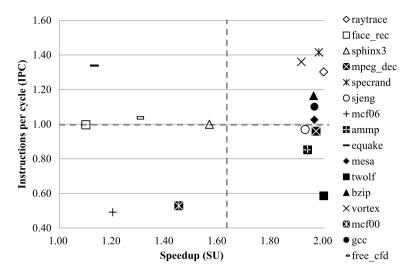

# 1.3.3 Behavior- and Architecture-Induced Temporal Slack: Runtime Distribution

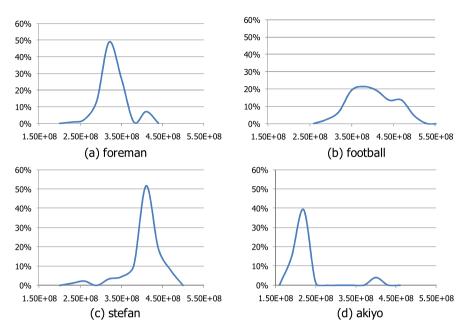

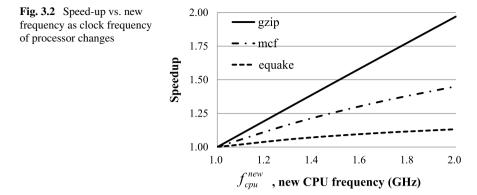

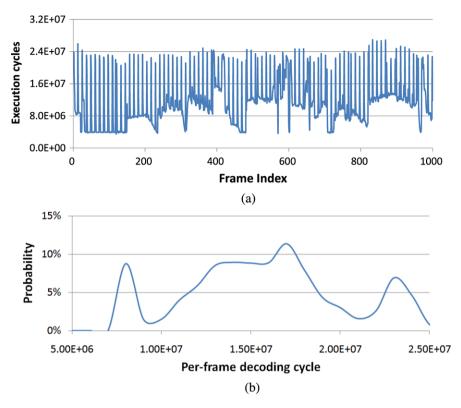

In existing DVFS methods based on the prediction of WCET, the operating frequency, i.e., operating voltage, is set to WCET/D where WCET is the worst case execution time of the remaining workload and D is the time to deadline. In reality, it is rare to encounter the WCET. Instead, the execution time tends to have a distribution. Figure 1.8 illustrates the distribution (probability density function) of the runtime in decoding video clips obtained by running JM8.5 on an ARM946EJ-S processor (SoCDesigner).

Given such a wide runtime variation, by running the processor at the frequency level targeted for the worst case, we will lose opportunities for further reduction in energy consumption. Intuitively, more energy reduction could be obtained by running the processor at a frequency level near the average execution time divided by the time to deadline as long as there is a measure to guarantee the satisfaction of the given deadline constraint [17].

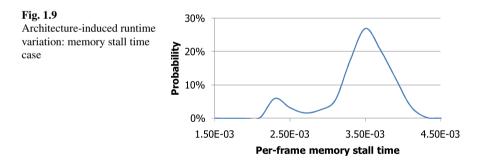

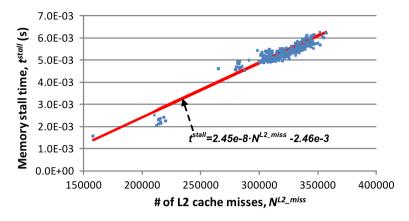

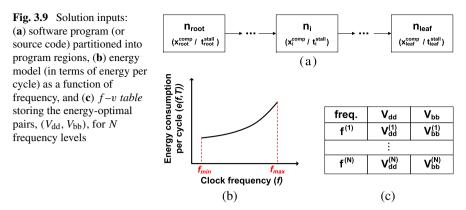

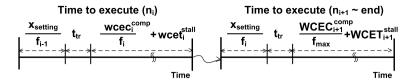

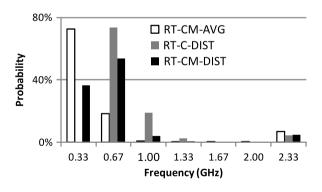

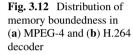

The runtime variation exemplified in Fig. 1.8 comes from two sources. One is the application behavior, which can have loops whose iteration counts are determined by input data. The other is the hardware architecture, the execution time of which varies depending on data values or access patterns. Figure 1.9 illustrates the distribution of the memory stall cycle obtained by running MPEG-4 decoding with 3000 frames of  $1920 \times 800$  *Dark Knight* on an LG XNOTE LW25 laptop [18]. Such a wide variation results from access locality in the L2 cache and DRAM. In this case, the worst case assumption on memory stall time leads to losing the opportunities for achieving better energy efficiency.

Fig. 1.8 Runtime variation in decoding different video clips

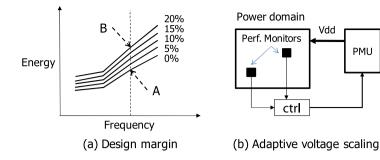

# 1.3.4 Process, Voltage, Temperature, and Reliability Slack

Determining a design margin is one of the most important issues in designing low power chips. Several kinds of variations are taken into account to determine the timing margin, including process, voltage, and temperature variations, which are called PVT variation. Recently, reliability, e.g., negative bias temperature inversion (NBTI) has also been included in the timing margin. The amount of timing margin to cope with such variations is confidential to each chip manufacturer. Typically, 10–20% of the timing margin is assumed. From the viewpoint of power consumption, a 20% timing margin represents an opportunity cost of 36% (=  $1 - 0.8^2$ ) reduction in power consumption, as Fig. 1.10(a) shows. The timing margin is used to cope with the worst case of each of the process, voltage, temperature, and relia-

PMU

Fig. 1.10 Coping with PVT variation [19]

bility variations. However, in reality, the worst case occurs only rarely. In addition, the four worst cases may occur at the same time with an extremely low probability. Thus, in normal conditions, the variations will be much smaller than the worst case levels. If we can exploit the slack, i.e., the difference between the worst and nominal conditions, we can recoup the lost opportunity cost.

Figure 1.10(b) illustrates how to exploit the slack dynamically during runtime. The figure shows a feedback loop starting from the performance monitor and going to the voltage regulator. The performance monitor mimics the critical path of the system with replica circuits. Based on the performance evaluation of the replica circuits, the performance monitor identifies the current level of process, voltage, temperature, and reliability variations. Based on the current performance level information, the controller (hardware or software) sets the voltage level to just meet the current operating frequency. Then, the voltage regulator adjusts the supply voltage (and body bias) to the level.

For instance, process variation can yield fast chips which have a lower threshold voltage than the average. The fast chips tend to suffer from high leakage power consumption due to the low threshold voltage. Thus, if the performance monitor reports that at the nominal voltage level (the voltage level obtained from the worst case assumption) the chip can run faster than the nominal frequency, then the supply voltage and/or body bias is reduced. As another example, if the current operating temperature is much lower than the worst case level, then a lower supply voltage than the nominal one is applied, thereby reducing the power consumption while meeting the required operating frequency. This method, called adaptive voltage scaling, is applied by most silicon manufacturers, for example, TI SmartReflex and ARM Intelligent Energy Manager.

# 1.3.5 Temporal and Spatial Thermal Slack

The increasing demand for computing power and the slow improvement in cooling methods drives the need for thermal management. Thermal management is required for both high performance and mobile computing. In high performance computing,

#### 1 Introduction

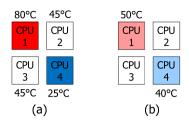

**Fig. 1.11** Exploiting two-dimensional thermal slack

as in the case of a data center, significant efforts are being made to lower the operation cost related to thermal management, i.e., cooling [2, 3, 5]. In mobile computing, thermal issues are considered from the beginning of the industrial design of the product in order to consider air flow inside the mobile devices, e.g., smartphones. In mobile computing, thermal constraints become more important for two reasons. First, there is no active cooling capability in mobile devices due to the small form factor requirement. Second, temperature has a significant impact on leakage power consumption; typically, leakage power consumption is exponentially proportional to temperature.

We can classify thermal slack as temporal and spatial slack. Temporal thermal slack represents the fact that a location on the silicon die can have phases of high and low operating temperature depending on the amount of computation, i.e., power dissipated in that location or nearby. At high temperatures, in order to prevent thermal problems, the execution is throttled or stopped. Thus, the lower the operating temperature, the higher the computing capability of the location. Adaptive voltage scaling, described above, is a way to exploit the temporal thermal slack.

Temperature reading is based on on-die temperature sensors. Multiple sensors monitor the temperature on hot spots (e.g., the instruction decoding stage, ALU, or floating point unit), and their maximum reading is typically interpreted as the core temperature. In real devices, significant temperature gradients exist on the die. For instance, even the intra-core temperature difference between the computing part and the cache exceeds 20°C [20].

Figure 1.11 illustrates how spatial thermal slack can be utilized for better energy efficiency. Figure 1.11(a) shows a quad-core example where CPU1 is the hottest while CPU4 is the coolest. In Fig. 1.11, suppose that a new thread needs to start on one of the four cores. Without considering the temperature gradient and the relationship between leakage power and temperature, any core with available computing power could be selected for the execution of the thread. However, for better energy efficiency, CPU4 needs to be selected because it is the coolest and will consume the least amount of energy by minimizing the leakage power, which is a strong function of temperature.

Temperature can determine the most energy-efficient core on the die, as shown in Fig. 1.11. The same situation occurs in the cases of 3D stacked dies on a small scale and the data center on a larger scale. In 3D stacked dies, the die near the heat sink has better cooling capability and thus is more energy efficient than other dies far from the heat sink. In the data center, computing server racks near the cooling facilities, e.g., at the air flow entrance, have a lower temperature and thus are more energy efficient than those with less cooling capability.

Fig. 1.12 Peak power slack-aware overclocking [21]

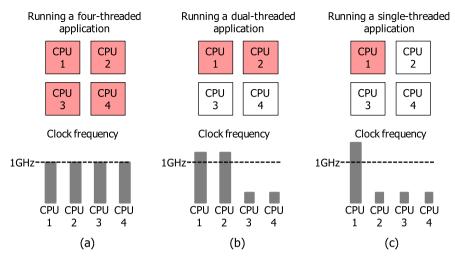

# 1.3.6 Peak Power Slack

The peak power constraint is the maximum power that the power delivery system can provide. The peak power slack is the difference between the peak power constraint and instantaneous power consumption drawn by the silicon die. The peak power slack is often exploited in order to maximize performance while meeting the given peak power constraint. Figure 1.12 shows an example of exploiting the peak power slack.

In Fig. 1.12(a), four CPUs run at 1 GHz a four-threaded application, thus, one thread on a core. In this case, the parallelism of quad-core is fully exploited, thereby giving the best energy efficiency. If there is less parallelism in the computation than that in the underlying architecture, we can exploit the peak power slack to boost the performance of lightly threaded applications. In Fig. 1.12(b), only two threads run on two cores. In this case, the clock frequencies and supply voltages of the running cores can be increased by fully utilizing the peak power constraint. Figure 1.12(c) shows the case of running a single-threaded application at a higher frequency than the nominal level. In terms of drawing maximum performance from the given power budget, such an overclocking is useful, as proven in commercial solutions, e.g., Intel Turbo Boost. However, the energy efficiency of this solution is not yet proven to be better than that of conventional clocking—an interesting issue for the general usage of this method.

# 1.3.7 Holistic Approach for More Slack and Better Ways to Exploit It

Because many methods for low power design utilize slack, discovering new types of slack will open new possibilities for better energy efficiency. We expect that more

types of slack and more innovative methods to exploit slack will be studied and applied to real designs. One possible way to discover new types of slack is a holistic approach which allows us to consider a bigger scope than a silicon chip design. One example that will be presented in this book is a surveillance system based on a wireless network where the quality of images captured in the camera subsystem and the transmission rate over the wireless network can be determined in an energy-efficient manner to realize the best quality of service (QoS) for the given budget of energy consumption. Another example of a holistic approach introduced in this book is the low power embedded storage system. In this system, dynamic power management by the storage subsystem only cannot fully exploit the full potential of existing idle time, i.e., slack in the storage subsystem. Instead, collaboration between the host and storage is required to better exploit the slack and thereby run the storage subsystem at lower power states more frequently, thus enabling less energy consumption.

# **1.4 Introduction to Chapters**

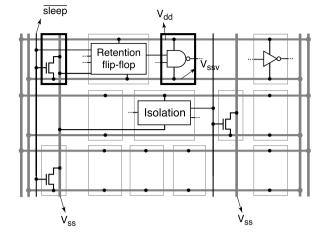

Chapter 2 introduces various low power circuit techniques. First, methods for power consumption and thermal analysis are presented. Then, low power circuit techniques are explained for reduction in dynamic power, such as clock gating and dual- $V_{dd}$  and static power, e.g., power gating and body biasing.

Chapter 3 explains software-level low power design methods. Low power design of software requires an understanding of the seemingly complex characteristics of software execution cycles, i.e., runtime distribution. In this chapter, a simplified processor power model is first presented. Then, runtime distribution-aware low power design methods are explained which take into account the variations of software execution cycles due to both software program behavior and hardware architecture.

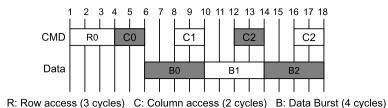

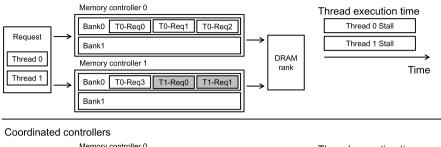

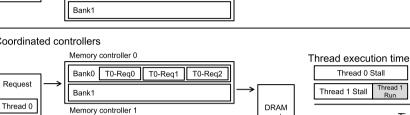

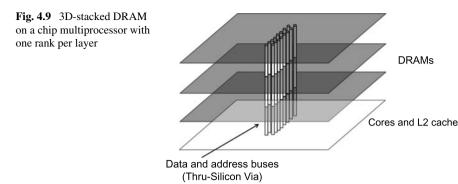

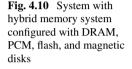

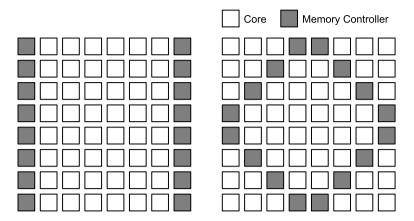

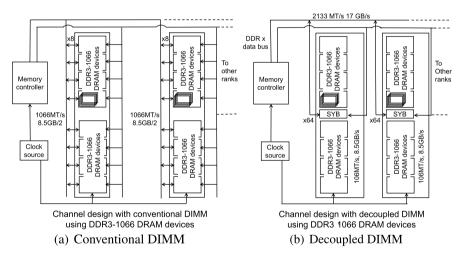

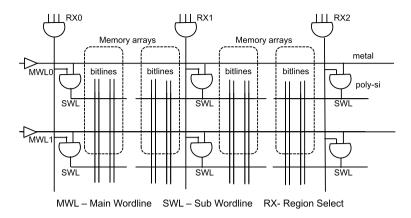

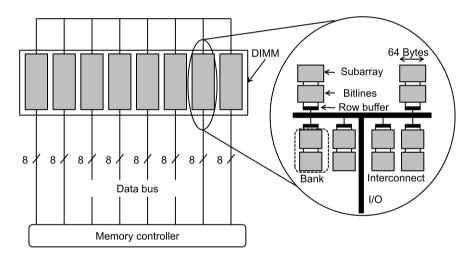

Chapter 4 reviews recent research efforts to improve the performance and energy efficiency of contemporary memory subsystems. First, memory access scheduling policies are explained, including conventional ones for performance and more advanced techniques for effectively managing DRAM power. Research works exploiting emerging technologies, e.g., 3D stacked DRAM and phase-change RAM, are introduced and their impacts on future memory subsystems are analyzed. Then, proposals to modify memory modules and memory device architectures are presented that reflect the memory access characteristics of future manycore systems.

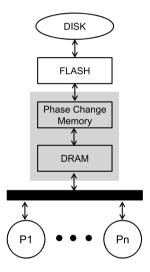

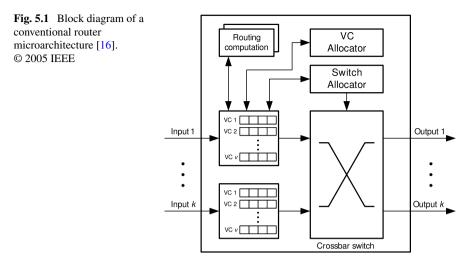

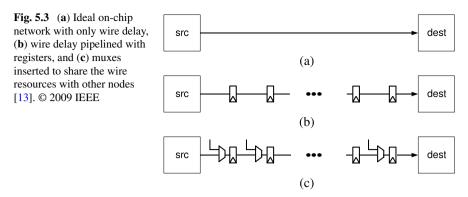

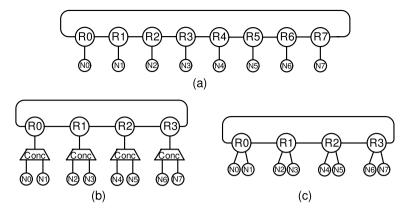

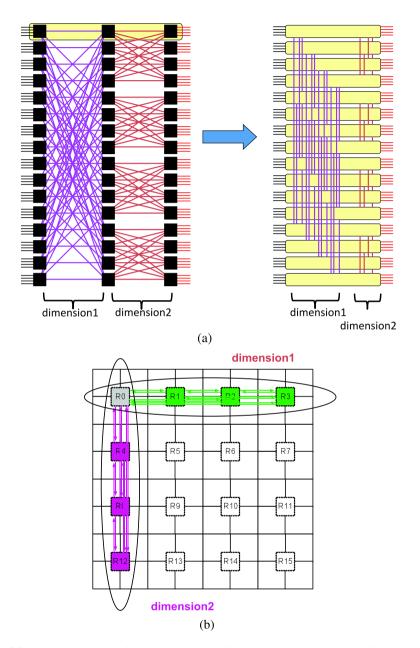

Chapter 5 addresses low power on-chip network design, which is required as manycore design is becoming more popular. It is projected that the on-chip network will be the critical bottleneck of future manycore processors—in terms of both performance and power. In this chapter, we focus on the characteristics of multi-core, manycore on-chip networks and describe how energy-aware on-chip networks can be achieved with different techniques. In particular, we focus on how ideal on-chip networks can be designed such that energy consumption can be minimized and approach the energy consumption of the wires or the channels themselves.

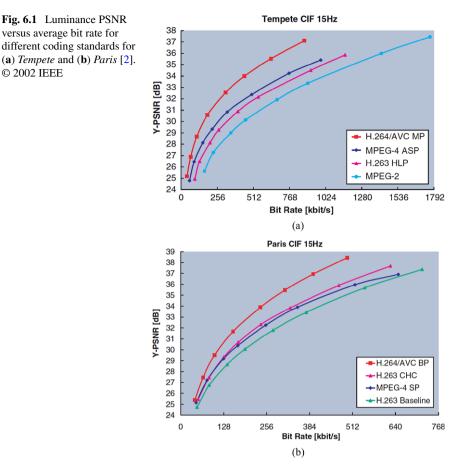

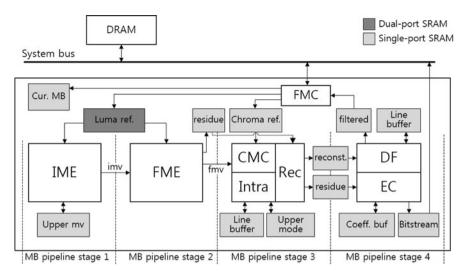

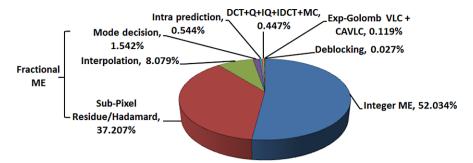

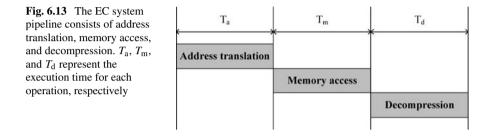

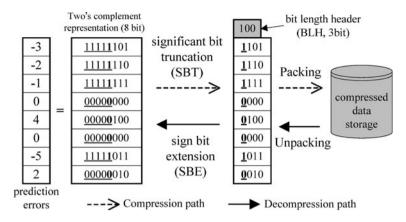

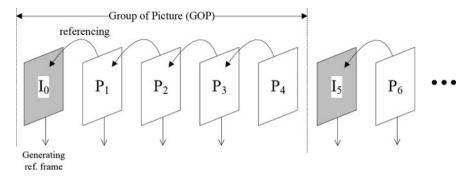

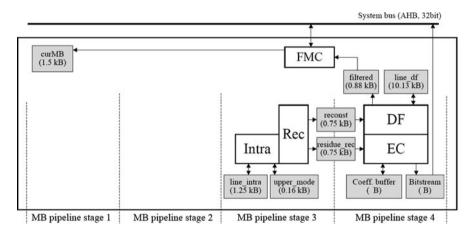

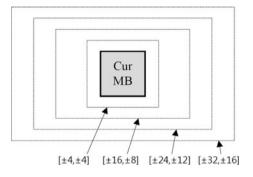

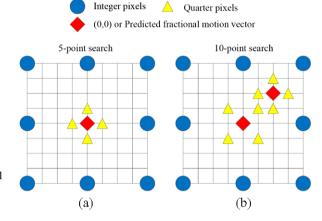

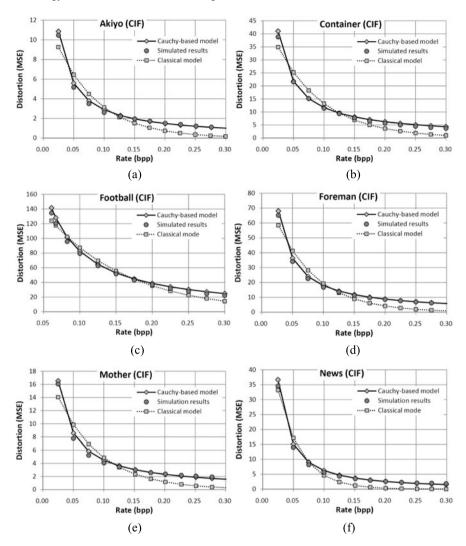

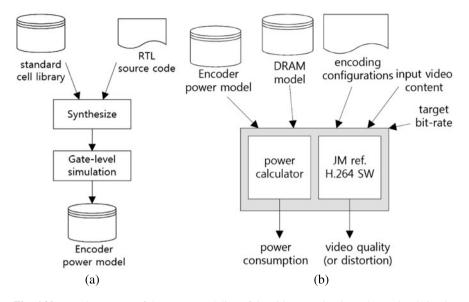

Chapter 6 presents an energy-aware video codec design. It consists of three parts: an implementation of a low power H.264/AVC video codec using embedded compression (EC), an architecture of a power-scalable H.264/AVC video codec, and a

power-rate-distortion modeling based on the power scalability of the video codec. The power consumption of the video codec results mainly from the external memory, i.e., DRAM, and the motion estimation (ME). In this chapter, the authors explain low power design techniques to reduce the power consumption of both DRAM and ME to offer about 80% reduction in the power consumption of the video codec.

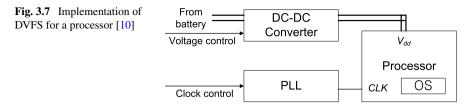

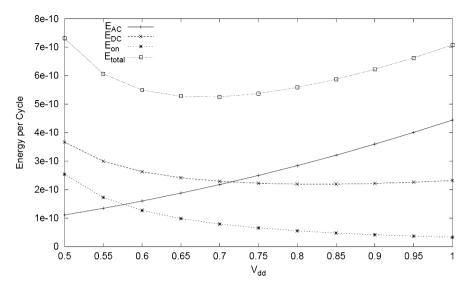

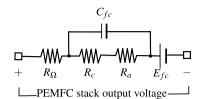

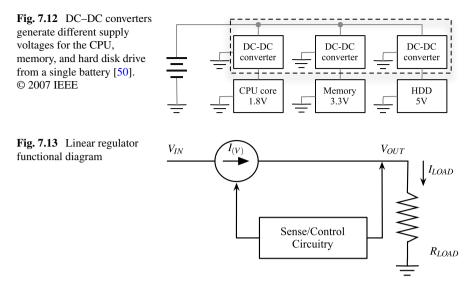

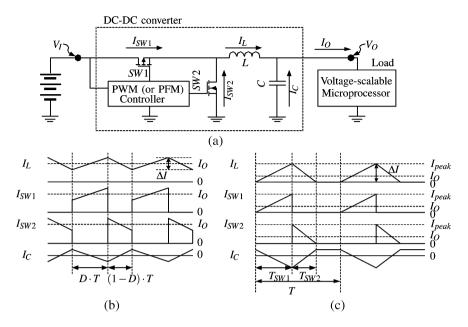

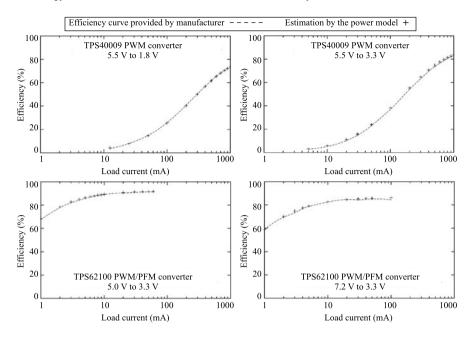

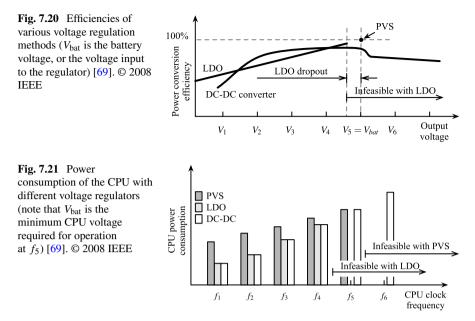

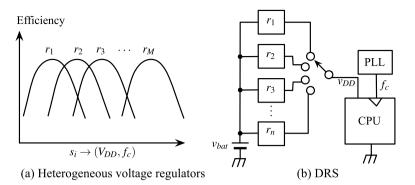

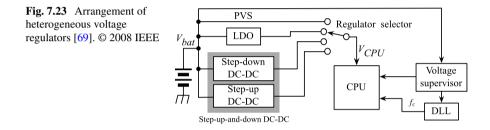

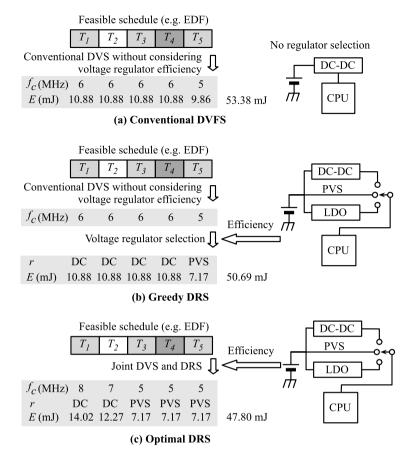

Chapter 7 explains that efficient power conversion and delivery is equally important for the energy efficiency of an entire system. Specifically, since different types of voltage sources are used in a system for both digital and non-digital parts, the power conversion efficiency of DC-DC converters and linear regulators is crucial to leverage the power efficiency of the entire system. This chapter introduces power conversion subsystems and their efficiency characteristics and discusses systemlevel solutions to leverage the power conversion efficiency.

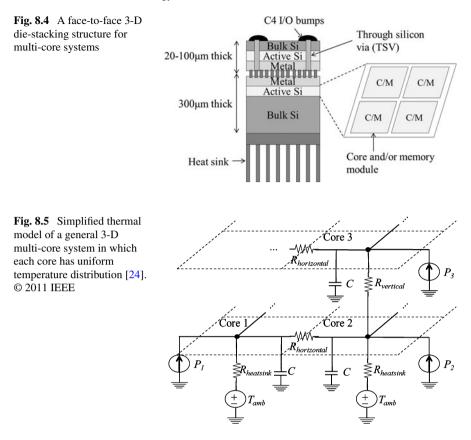

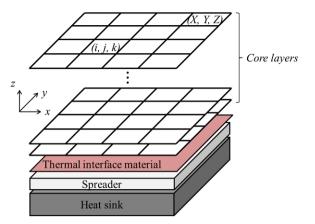

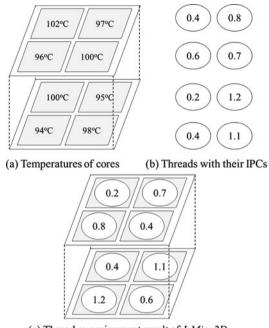

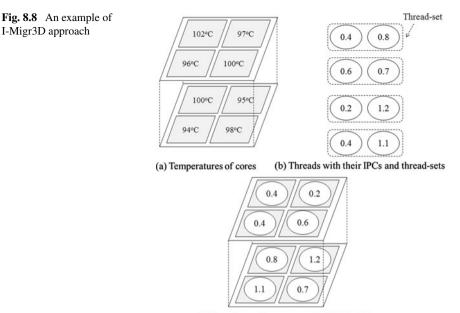

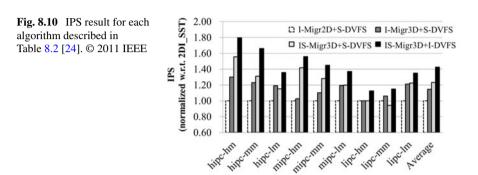

3D stacking of silicon dies presents a new low power design challenge coupled with that of temperature. In Chap. 8, the authors present a temperature-aware low power design method for 3D ICs. First, the characteristics of strong vertical thermal coupling in 3D die stacking are exploited to ease function mapping on cores. The authors describe two ideas: instantaneous temperature slack and memory boundedness-aware thread mapping. Instantaneous temperature slack enables one to overcome the conservatism in existing methods based on steady-state temperature, thereby enabling more aggressive utilization of temperature slack during runtime. Memory-bound threads are less sensitive to the core clock frequency change. Thus, the authors propose mapping memory-bound threads on hot and slow cores, which usually lack cooling capability since they are far from the heat sink. This choice enables CPU-bound threads to be mapped on cool and fast cores near the heat sink, thereby improving the total system performance.

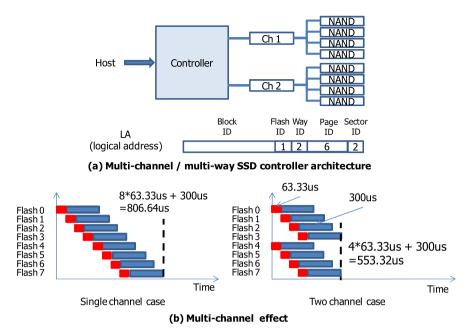

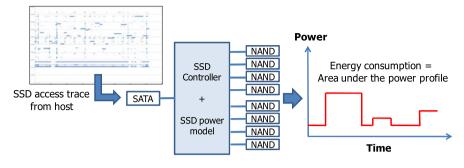

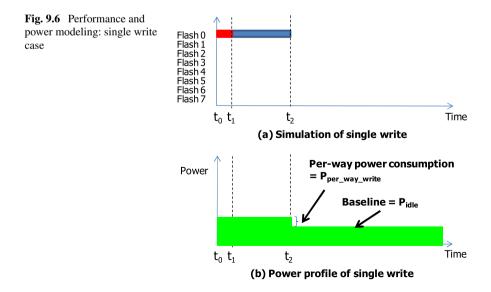

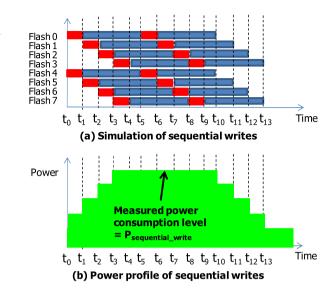

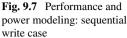

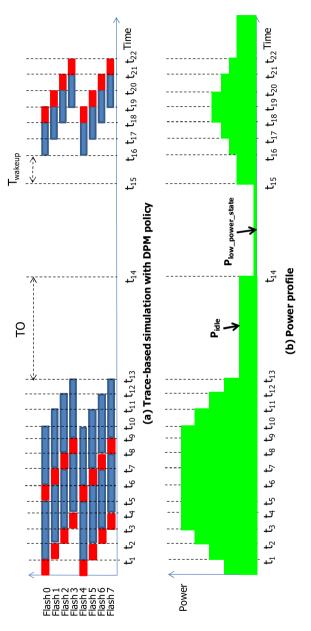

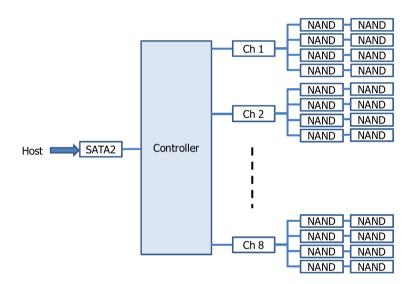

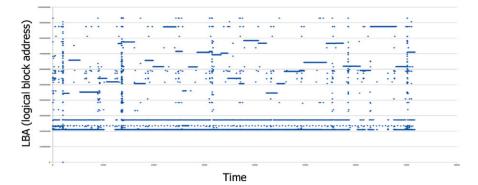

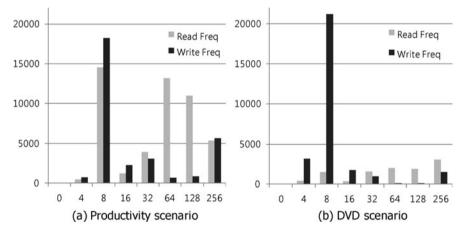

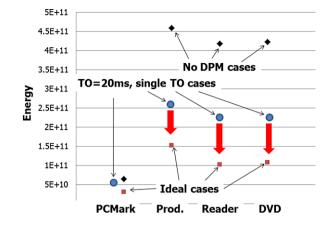

Chapter 9 presents a case study of low power solid state disk (SSD) design. The chapter first introduces a multi-channel architecture for a high performance SSD. It then presents a power model of the SSD considering the parallel operations in the multi-channel architecture. It also gives an example in which the SSD power model is used to evaluate time out-based dynamic power management policies.

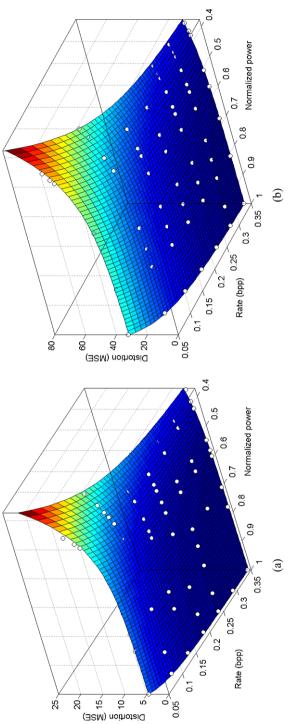

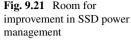

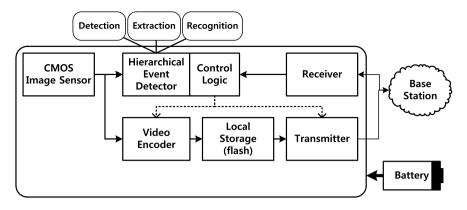

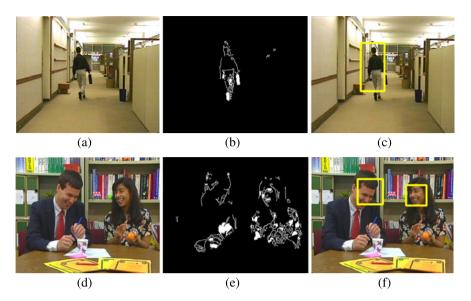

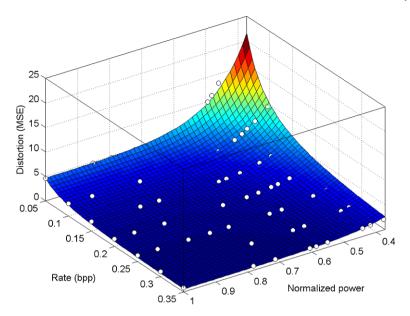

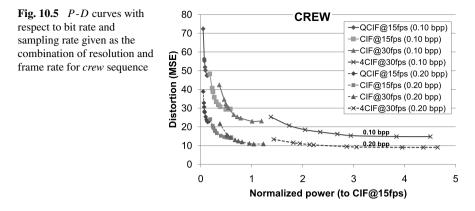

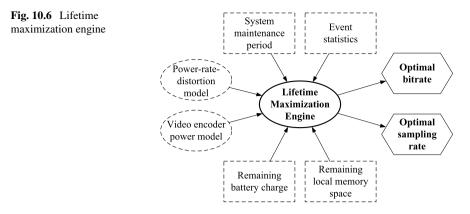

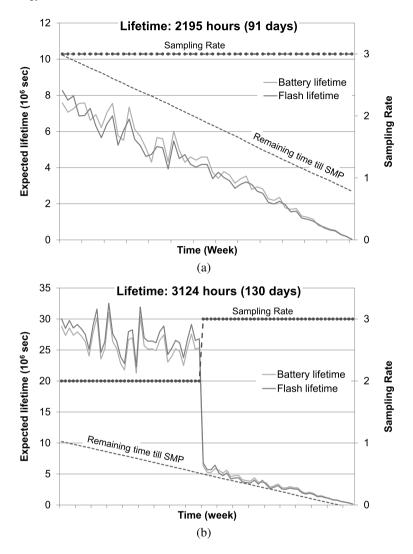

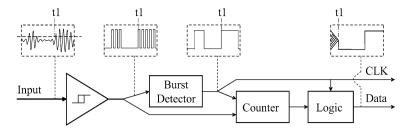

Chapter 10 gives an energy-aware design example of a wireless surveillance camera (WSC) consisting of image sensor, event detector, video encoder, flash memory, wireless transmitter, and battery. It is based on hierarchical event detection and data management (e.g., local store or remote transmission) to save the energy otherwise wasted on insignificant events. In a WSC, balancing the usage of all resources including battery and flash memory is critical to prolonging the lifetime of the camera, because a shortage of either battery charge or flash memory capacity could lead to a complete loss of events or a significant loss in the quality of the recorded image of events. The authors present a novel method which controls the bit rate of encoded videos and the sampling rate, e.g., the resolution and frame rate, to prolong the lifetime of the WSC.

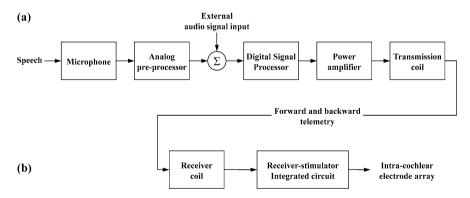

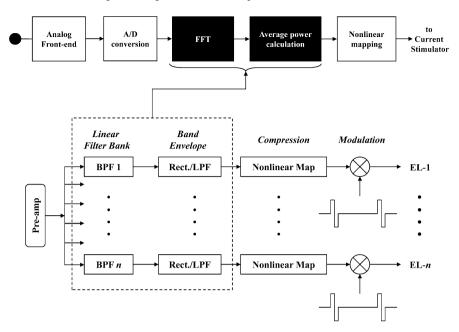

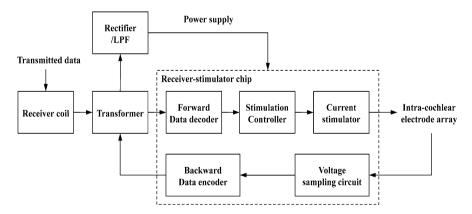

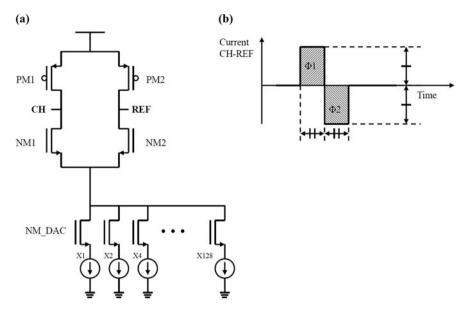

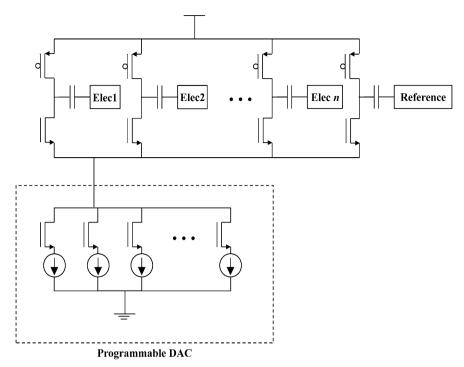

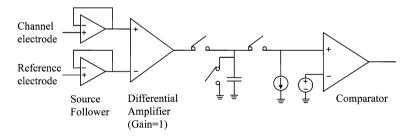

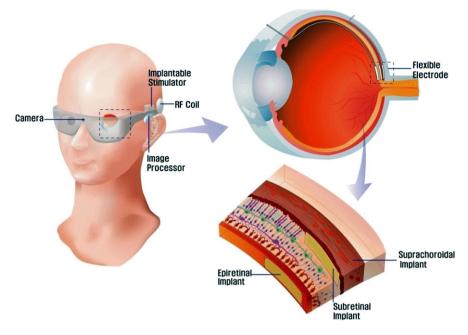

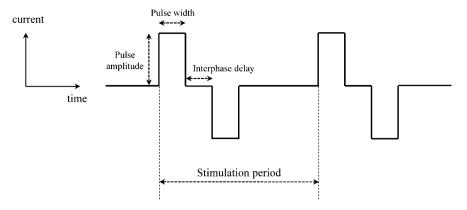

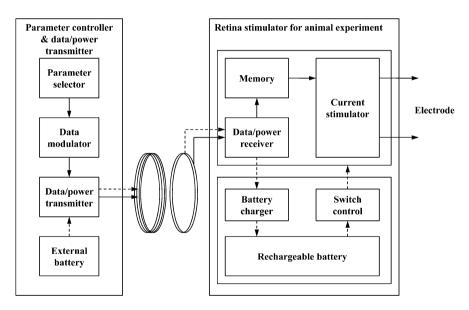

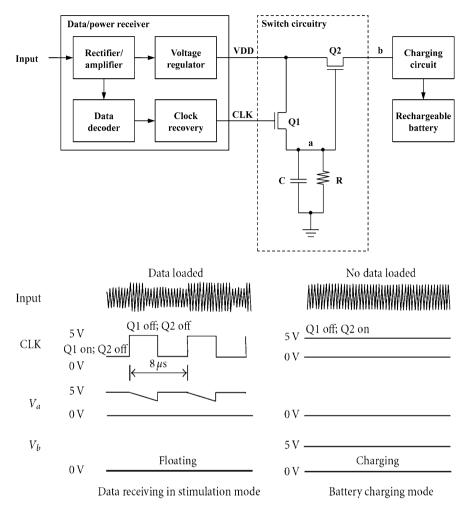

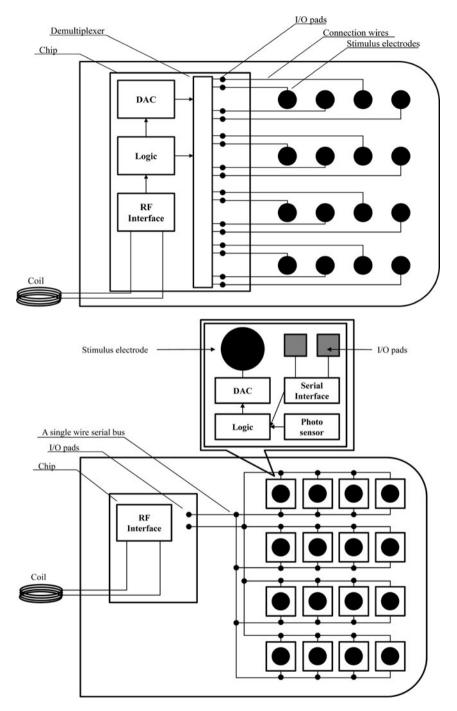

Chapter 11 discusses two IC design examples for biomedical implantable electronics: cochlear and retinal implants. Energy and power awareness is important in such devices for safety as well as battery lifetime. For example, the pulsed output waveforms for electrical stimulation in such implants should be charge-balanced, because any unbalanced charge, if accumulated beyond a safe limit, can lead to cell damage and electrode corrosion. The chapter also addresses the issue of the longterm reliability of a neural interface whose impedance changes over a long time, therefore requiring monitoring-based adjustment of stimulation parameters to make sure that an optimum amount of electrical charge is delivered to the target neurons.

# References

- 1. International Technology Roadmap for Semiconductor. http://www.itrs.net

- US Environmental Protection Agency: Report to congress on server and data center energy efficiency public law 109-431, Aug. 2007

- 3. McKinsey & Company: Revolutionizing data center energy efficiency, July 2008

- 4. Hamilton, J.: Data center infrastructure innovation. In: Web Performance and Operations Conference (Velocity), June 2010

- Meisner, D., Gold, B.T., Wenisch, T.F.: PowerNap: eliminating server idle power. In: International Conference on Architectural Support for Programming Languages and Operating Systems (2009)

- Intel, Co.: Data center energy efficiency with Intel<sup>®</sup> power management technologies, Feb. 2010

- Neuvo, Y.: Cellular phones as embedded systems. In: Proceedings of IEEE International Solid-State Circuits Conference (2004)

- Van Berkel, C.H.: Multi-core for mobile phones. In: Design Automation and Test in Europe (2009)

- 9. Wikipedia: Energy density. http://en.wikipedia.org/wiki/Energy\_density

- Flynn, D., Aitken, R., Gibbons, A., Shi, K.: Low Power Methodology Manual: For Systemon-Chip Design. Springer, Berlin (2007)

- 11. Efficient Computing at Google. http://www.google.com/corporate/green/datacenters/ index.html

- 12. Rabaey, J.: Low Power Design Essentials. Springer, Berlin (2009)

- 13. ARM Ltd.: Processors. http://www.arm.com/products/processors/index.php

- 14. Azevedo, A., et al.: Profile-based dynamic voltage scheduling using program checkpoints. In: Design Automation and Test in Europe (2002)

- Bang, S., Bang, K., Yoon, S., Chung, E.Y.: Run-time adaptive workload estimation for dynamic voltage scaling. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 28(9), 1334– 1347 (2009)

- Naveh, A., et al.: Power and thermal management in the Intel core duo processor. Intel Technol. J. 10(2) (2006)

- 17. Hong, S., et al.: Runtime distribution-aware dynamic voltage scaling. In: International Conference on Computer-Aided Design (2006)

- Kim, J., Yoo, S., Kyung, C.M.: Program phase-aware dynamic voltage scaling under variable computational workload and memory stall environment. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 30(1), 110–123 (2011)

- 19. National Semiconductor, Co.: PowerWise Adaptive Voltage Scaling (AVS). http://www.national.com/analog/powerwise/avs\_overview

- Schmidt, R.: Power trends in the electronics industry—thermal impacts. In: IBM Austin Conference on Energy-Efficient Design (2003)

- 21. Intel, Co.: Inter turbo boost technology 2.0. http://www.intel.com/technology/product/ demos/turboboost/demo.htm

# Chapter 2 Low-Power Circuits: A System-Level Perspective

Youngsoo Shin

**Abstract** Popular circuit techniques for reducing dynamic and static power consumption are reviewed. The emphasis is on the implication when they are applied, e.g., area increase, because this may serve as important information during systemlevel design. The estimation of power and temperature is also reviewed.

# 2.1 Introduction

During the architectural design (or system-level design, broadly speaking), a lot of what-if questions are likely to be raised and answered. For example, in a network processor, the designers may consider employing two Ethernet controllers, instead of a single one, to improve throughput, but may also want to validate the choice in terms of chip area [1].

Due to the growing importance of power consumption, it is now tempting to assess the design choice in terms of power: what happens if clock gating is applied to block A, which contains many synchronous memory elements; what happens if body biasing is used in block B, which stays in standby mode for most of its operation time? These questions should be answered after the implication of applying each circuit technique is precisely understood from a system-level perspective; e.g., how much does the circuit area increase when clock gating is applied to A, and what is the latency to put B in standby mode and bring it back to active mode?

This chapter is organized to review various low-power circuit techniques from a system-level perspective. A technique to estimate power consumption is discussed in Sect. 2.3; thermal analysis, which has become very important, is also addressed. Power consumption can be categorized into dynamic power during operational time and static power during standby periods. Representative circuit techniques to reduce the dynamic component, i.e., clock gating and dual- $V_{dd}$ , as well as other techniques are reviewed in Sect. 2.4. Techniques to reduce the static component, such as power gating and body biasing, are presented in Sect. 2.5.

Y. Shin (🖂)

KAIST, Daejeon, Republic of Korea

e-mail: youngsoo@ee.kaist.ac.kr

## 2.2 CMOS Power Consumption

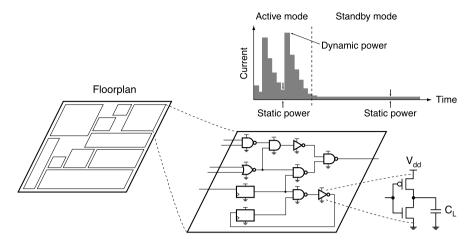

To understand the nature of power consumption of CMOS circuits, consider the chip floorplan illustrated in Fig. 2.1. The overall operation of a floorplan block can be classified as being in active or in standby mode. Active mode refers to the period of time when the block is actively computing to produce valuable output; the remaining period is called standby mode. In active mode, there are two components of power consumption: dynamic and static power. *Dynamic power* is consumed while a transistor is switching. The length of time that it switches is usually a small proportion of a clock cycle; for the remaining time, the transistor consumes *static power*. Standby mode, which does not involve any transistor switching, consists of static power alone (assuming that there is also no switching activity in a clock). It is important to understand that the static power in active mode is a transient one, while that in standby mode is a static one; therefore, their amounts are very different, as we address later in this section.

#### 2.2.1 Dynamic Power

While the output of the CMOS inverter shown in Fig. 2.1 makes a pair of rising and falling transitions, the amount  $C_L V_{dd}^2$  of energy is dissipated, half of it by the pMOS transistor and the other half by the nMOS transistor.  $C_L$  is the load capacitance, which models the gate capacitance of fanout gates, the wire capacitance, and the intrinsic capacitance of the inverter itself.

The average power consumption due to the switching, which is the total energy dissipation during a particular period of time divided by the length of that period, is given by the well-known expression

$$P_{\rm sw} = \alpha C_{\rm L} V_{\rm dd}^2 f, \qquad (2.1)$$

where f is the clock frequency and  $\alpha^1$  is the probability of the output making a pair of rising and falling transitions in a single clock cycle. Note that  $\alpha \le 0.5$  for any combinational gate unless there is a glitch; in practical circuits,  $\alpha$  turns out to be very low, typically less than 0.05. Gates that are driven by a clock, for example those in clock buffers, have  $\alpha = 1.0$ .

Another component of dynamic power consumption, denoted by  $P_{sc}$ , is caused by *short-circuit current*. This is the current that flows while both the nMOS and pMOS transistors are turned on for a short period of time when the input signal makes a transition (from 0 to 1 or 1 to 0). Interestingly,  $P_{sc}$  decreases with increasing  $C_L$  [2], because the output, which changes its value more slowly when heavily loaded, keeps the short-circuit current from increasing.  $C_L$ , however, cannot be arbitrarily increased due to increased circuit delay.  $P_{sc}$  is usually pre-characterized

<sup>&</sup>lt;sup>1</sup>Some people use  $\alpha$  as a probability that the output makes a transition (either rising or falling) rather than a pair of transitions. With this definition,  $1/2\alpha$  would be used instead of  $\alpha$  in (2.1).

Fig. 2.1 Power consumption of an architectural block

when each gate is designed and is available during power estimation. In practical circuits,  $P_{sc}$  is a small proportion of the total dynamic power consumption  $P_{dyn}$ ; e.g.,  $P_{sc}/P_{dyn}$  is estimated to be about 10% [3].

# 2.2.2 Static Power

The static power consumption is a result of the device leakage current, which originates from various physical phenomena [4]. Three components of leakage (subthreshold, gate tunneling, and junction leakage) get more attention than the other ones due to their large proportion in the total static power. The relative importance of these components differs with the technology, the temperature, the style of the circuit, and so on. For instance, gate leakage is important in static random access memory (SRAM) circuits since they typically rely on devices of larger gate length to reduce random dopant variations, while subthreshold leakage is dominant in logic circuits [5].

The subthreshold leakage occurs when the gate-to-source voltage of a transistor is below its threshold voltage ( $V_{\text{th}}$ ), i.e., when a device is presumed to be turned off. It is well known that this leakage component increases exponentially with decreasing  $V_{\text{th}}$ , increasing temperature, and increasing gate-to-source voltage. This implies the growing importance of subthreshold leakage as CMOS technology scales down, since  $V_{\text{th}}$  tends to decrease to maintain circuit speed. It also implies that any quantitative result on static power should be carefully understood; e.g., the value may be very different for different temperatures.

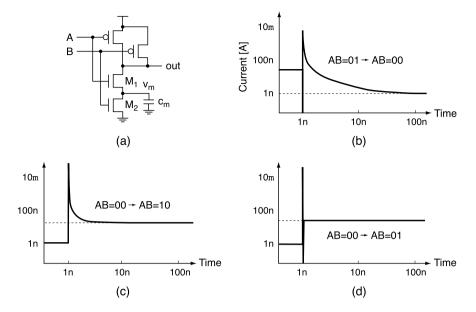

The standby leakage (leakage in standby mode) of the 2-input NAND gate shown in Fig. 2.2(a) for the different inputs is given in the second column of Table 2.1. It is well known that this leakage is lowest when the input is 00, as Table 2.1 confirms.

Fig. 2.2 (a) A 2-input NAND gate: active leakage for input transitions (b) from 01 to 00, (c) from 00 to 10, and (d) from 00 to 01

| <b>Table 2.1</b> Standby andactive leakage of a 2-input | Input | Standby      | Active leakage (nA) |      |       |  |

|---------------------------------------------------------|-------|--------------|---------------------|------|-------|--|

| NAND gate in 45-nm<br>technology                        | (AB)  | leakage (nA) | 1 ns                | 5 ns | 10 ns |  |

|                                                         | 00    | 1.0          | 11.2                | 3.0  | 1.9   |  |

|                                                         | 01    | 16.6         | 16.2                | 16.6 | 16.6  |  |

|                                                         | 10    | 10.3         | 17.7                | 10.4 | 10.3  |  |

|                                                         | 11    | 26.4         | 26.4                | 26.4 | 26.4  |  |

|                                                         |       |              |                     |      |       |  |

The reason is that there is a positive voltage  $v_m$  which builds up between  $M_1$  and  $M_2$  and turns  $M_1$  off strongly, due to a negative gate-to-source voltage; this voltage also raises the effective threshold voltage of  $M_1$ . The whole phenomenon is called the stacking effect [6], because the leakage shrinks as stacked MOS transistors are turned off.

We now turn our attention to active leakage (leakage in active mode). When the input is maintained at 01, the internal node capacitance  $c_m$  is fully discharged. If the input is changed to 00 after 1 ns, as depicted in Fig. 2.2(b), the small leakage current through M<sub>1</sub> starts to charge  $c_m$ . As  $v_m$  rises, the leakage through M<sub>1</sub> falls further due to the stacking effect. But this transition takes a long time, as shown in Fig. 2.2(b). The effect on leakage of a change of input from 00 to 10 is shown in Fig. 2.2(c). The large turn-on current through M<sub>1</sub> initially charges  $c_m$ ; however, as  $v_m$  rises, M<sub>1</sub> turns off, but then its leakage current takes over and continues to charge  $c_m$ , even though the leakage is gradually falling. If M<sub>2</sub> is turned on, for instance by

the change of input from 00 to 01 shown in Fig. 2.2(d), the corresponding leakage transition is virtually spontaneous since  $c_m$  is quickly discharged.

The average active leakage over different periods after the change of input value is given in the last three columns of Table 2.1. Each value is also averaged over all the transitions that lead to the inputs shown in the first column: thus the first row covers transitions from 01 to 00, from 10 to 00, and from 11 to 00.

The standby and the active leakage are about the same when a 1 is applied to input B (01 and 11 of Table 2.1), which turns on  $M_2$ . The leakages for 10 and, especially, 00, are significantly different, particularly for the period immediately after the transition, implying a higher operating frequency.

# 2.2.3 Analysis

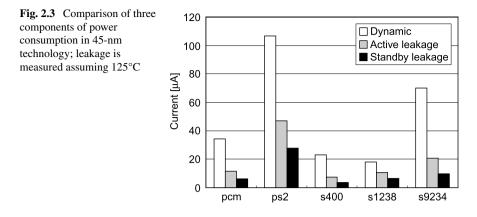

There are now three components of power consumption: dynamic, active leakage, and standby leakage. The first two components are sources of active-mode power consumption; the last defines standby-mode power consumption. Experiments were performed in 45-nm technology to understand the relative measure of the components; the results are shown in Fig. 2.3. Example circuits were taken from International Symposium on Circuits and Systems (ISCAS) benchmarks as well as from OpenCores [7]. The current was obtained by applying 100 random vectors; the clock period was arbitrarily assumed at 5 ns.

Active leakage represents, on average, 28% of the total active-mode power consumption; it is as high as 37% in s1238 and as low as 23% in s9234. Note that the leakage was measured in conditions where it becomes as large as possible, i.e., a fast process corner in which  $V_{\text{th}}$  is smallest and at the highest operating temperature. Since dynamic power is scarcely affected by these parameters, the proportion of active leakage will become smaller in different conditions. For example, its proportion decreases to 14% in a nominal process corner with the same temperature.

The average standby leakage is 54% of the average active leakage. The variation in the leakage ratio between circuits can be explained by the extent of the stacking

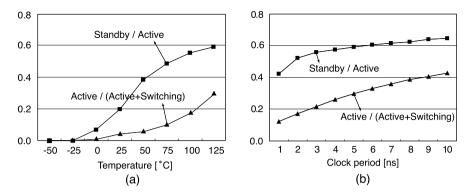

Fig. 2.4 Ratio of standby to active leakage, and the proportion of active leakage in circuit ps2: with (a) varying temperature and (b) varying clock period

effect in each circuit. When there are more gates that exhibit the stacking effect in standby mode, we expect the difference between active and standby leakage to increase. This can be confirmed by counting the number of inverters and flip-flops, which are representative of the gates without the stacking effect.

The proportion of active leakage decreases with temperature, as shown in Fig. 2.4(a). The ratio of standby to active leakage also declines, as Fig. 2.4(a) shows, suggesting that the importance of active leakage grows as the temperature drops. When this happens, the transient change in active leakage due to a transition (see Fig. 2.2) takes longer because of its reduced magnitude, which means that  $c_m$  is charged more slowly: this increases the difference between active and standby leakage.

As the clock frequency increases and the clock period decreases, the magnitude of the active leakage will increase while the standby leakage remains the same. This is evident from the decreasing ratio between the standby and active leakage shown in Fig. 2.4(b). The total switching current is independent of the clock period, as long as that period is sufficient to accommodate all the switching required. While the average switching current and the active leakage both increase as the clock period decreases, the average switching current increases more rapidly. Thus, the active leakage comes to represent a lower proportion of the total active-mode current, as we see in Fig. 2.4(b).

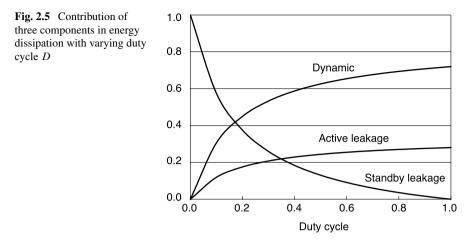

The contribution of the three components in energy dissipation is determined by the amount of time for which each component is responsible. This in turn is dependent on the fraction of time a circuit stays in active mode, i.e., the duty cycle D. Let dynamic power and active leakage be 72% and 28% of the active-mode power consumption, respectively, and active leakage be 1.87 times the standby leakage. Figure 2.5 illustrates the contribution of the three components with different values of D, e.g., 4.80D/(5.67D + 1) for dynamic power. When D = 0.1 such as in a cell phone, 58% of the energy is due to standby leakage, while 31% and 11% are due to dynamic and active leakage. It is apparent that most of the energy is dissipated by dynamic power as D increases, which arises in stationary devices such as servers.

# 2.3 Estimation of Power Consumption

The biggest part of answering what-if questions during architectural design is the ability to estimate power consumption, before and after a particular circuit technique is applied; this is a subject of this section. We also address temperature estimation because the main quantity that determines temperature is power consumption and because temperature has become a roadblock in technology scaling.

#### 2.3.1 Dynamic Power

Expression (2.1) suggests that the estimation of  $P_{sw}$  comes down to estimating  $\alpha$  of each node, once  $C_L$  is extracted. This is done either by simulation or by probabilistic analysis.

Different gate delay models can be used in a simulation approach. The simplest model assumes zero gate delay for the sake of simulation time. Each gate can have at most one transition per input vector, since all transitions occur at the same time. If real delay is used, each gate may have different delay resulting in different arrival times at the gate inputs, which causes more than one transition per input vector. But, this takes more time than simulation under zero delay. Gate-level simulation is reported to yield an error of  $\pm 15\%$  compared to circuit-level simulation, which exhibits  $\pm 5\%$  error [8]. Another issue is the preparation of input vectors. This is either done by designer-specified use scenarios, or is based on generating a sequence of random vectors. The interesting question here is the number of vectors that should be provided for reasonable accuracy. Experimental study [8] states that using any 100 or 10 consecutive vectors guarantees an error within  $\pm 5\%$  or  $\pm 15\%$  (compared to using the whole sequence of vectors from use scenarios), which implies that 10 should be enough for the accuracy of gate-level simulation.

Probabilistic analysis is more convenient from a designer's perspective. One may simply assume a signal probability (probability of signal being at 1) at each circuit input, quite often 0.5. The probabilities are then propagated toward circuit outputs. The propagation of independent signals is straightforward; e.g., the signal probability at the output of an AND gate is 0.25 when the signal probability of both inputs is 0.5. However, in general circuits, many signals are not independent due to reconvergent fanout; i.e., the same fanout converges at the same gate after going through different paths to the gates. The propagation in this case becomes more difficult, although several methods have been proposed [9].

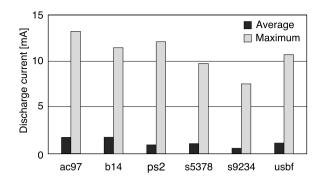

Note that these power estimation methods target average power consumption. The maximum power consumption, which is necessary for designing a power distribution network, is significantly larger than the average one. This is quantitatively shown for several circuits in Fig. 2.6, in which the difference ranges from 6 to 7 times.

Accuracy of Estimation The important issue in power estimation is its accuracy. This is affected by several factors such as delay model, wire model, and test vectors, but, more importantly, by the design stage in which power estimation is performed. During system-level design, many blocks are in a register transfer level (RTL) description. The description then goes through logic synthesis, in particular technology mapping, to obtain a technology-mapped netlist; some optimizations are then performed, and the layout is finally obtained. Before layout design, the inaccuracy of power estimation ranges  $\pm 15\%$ ; a similar inaccuracy is observed in power estimation before optimization. However, the error of power estimation before technology mapping (an estimation without actual netlist) can reach a factor of 4 or 10, which invalidates any estimation effort at that early stage [8].

# 2.3.2 Static Power

For a given gate-level netlist, estimating leakage power is generally more difficult than estimating switching power. Switching power is weakly dependent on device

parameters and operating environments. However, leakage power is strongly affected by the variations of process parameters (e.g., gate length, oxide thickness, and channel dose), variations of operating environment (temperature and  $V_{dd}$ ), and different input patterns.

The dependency of leakage current on process variations is the strongest; e.g., for  $3\sigma$  die-to-die V<sub>th</sub> variation of 30 mV in 180-nm CMOS technology, the leakage current can vary by a factor of 20, while the frequency varies only by 20% [10]. Die-to-die variations are typically taken into account by using process corners; i.e., we can estimate leakage current by assuming one particular set of deterministic device parameters. However, within-die variations, which are occupying an increasing proportion of total process variations with technology scaling, can only be captured by statistical estimation. The dependency of leakage on operating environments is also strong, although less strong than for process variations in practice. Leakage has a superlinear dependency on temperature, e.g., a 30°C change of temperature causes leakage to increase by 30%, and its dependency on supply voltage is exponential, e.g., a 20% fluctuation of  $V_{\rm dd}$  causes leakage to change by a factor of 2 or more [11]. Therefore, for accuracy, leakage estimation should be coupled with an analysis of temperature and  $V_{dd}$  distribution. The dependency of leakage on input vectors is strong in individual gates, but becomes very weak in whole circuits, especially as circuits have more levels due to lack of controllability.

**Static Estimation** For leakage analysis or simulation, each gate in the library must be characterized in its leakage. For example, for a 2-input NAND gate, the leakage for each input combination can be characterized:  $L_{00}$ ,  $L_{01}$ ,  $L_{10}$ ,  $L_{11}$ , where  $L_{ij}$  indicates leakage when the inputs take *i* and *j*. Alternatively, for simplicity, its leakage could be characterized by the average value.

If the leakage of all the gates is characterized, the leakage of an individual gate can be obtained if we know the signal probability of each input. For example, the leakage of the 2-input NAND gate is given by  $(1 - p_1)(1 - p_2)L_{00} + (1 - p_1)p_2L_{01} + p_1(1 - p_2)L_{10} + p_1p_2L_{11}$ , where  $p_1$  and  $p_2$  are the signal probabilities of two inputs. The leakage of the whole circuit can then be obtained by summing all the leakages. Thus, the key step is to derive the signal probability of all internal nodes given the signal probability of the primary input, which is the same process as in dynamic power estimation.

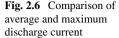

**Statistical Estimation** There are two methods to incorporate within-die process variation in leakage analysis: Monte Carlo simulation (simulation with repeated random sampling of variation source) or statistical estimation. Figure 2.7 illustrates typical leakage histograms after Monte Carlo simulation with 45-nm technology [12], in which  $\sigma$  of  $V_{\text{th}}$  is assumed to be 10% of its normal value. The histogram roughly follows a lognormal distribution.

In statistical estimation, the leakage of each gate is modeled as a lognormal, i.e.,  $\alpha e^{Y_i}$  [13], where  $Y_i$  is a function of process parameters such as gate length and gate oxide thickness, and approximated as a normal distribution. It is shown that both subthreshold and gate tunneling leakage follow this model. The full-chip leakage is then a sum of lognormals, which can be approximated as another lognormal

Fig. 2.7 Monte Carlo simulation of leakage: (a) c432 and (b) c1350

or, more accurately, as an inverse-gamma distribution [14]. If leakage is estimated from a layout, a spatial correlation of device parameters must be taken into account. In other words,  $Y_i$  and  $Y_j$  are highly correlated if gates *i* and *j* are closely located. A chip is divided into an imaginary grid, and a correlation coefficient is defined between a pair of grids, which is then incorporated into the leakage estimation [13].

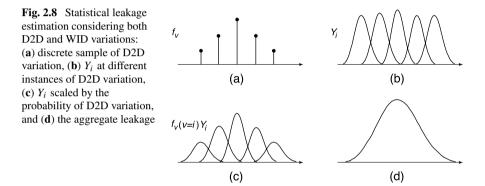

Statistical leakage estimation considering both die-to-die (D2D) and within-die (WID) variations can be done, as illustrated in Fig. 2.8 [15]. D2D variation is sampled at discrete points (a). Each sampled value becomes a mean of a corresponding normal distribution of  $Y_i$  (b). Each  $Y_i$  is scaled by the corresponding probability of the sample from D2D space (c). Statistical leakage estimation is done for each  $Y_i$  and aggregate leakage is obtained (d).

# 2.3.3 Temperature Estimation

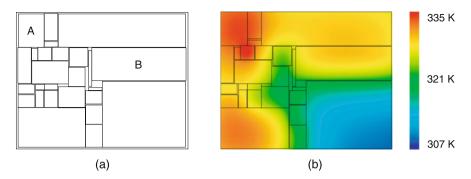

Temperature changes because of the convection of heat. Therefore, it is reasonable to expect to produce temperature change by adjusting the location of hotter and colder blocks, i.e., by trying different floorplans. It is reported that different floor-

Fig. 2.9 (a) Floorplan of an example chip and (b) thermal map

plans of microprocessors can yield a difference of maximum temperature of as high as 37°C [16].

For a given floorplan, as shown in Fig. 2.9(a), the following heat conduction equation is solved to generate a thermal map, shown in Fig. 2.9(b):

$$\rho C_{\rm p} \frac{\partial T(x, y, z, t)}{\partial t} = \nabla \left[ \kappa(x, y, z, t) \nabla T(x, y, z, t) \right] + g(x, y, z, t), \qquad (2.2)$$

where *T* is the temperature which we try to obtain, *g* is the power density of a heat source, and  $\kappa$  denotes thermal conductivity;  $\rho$  and  $C_p$  are material-dependent parameters. Physically, (2.2) implies that the energy stored in a volume *V* (left-hand side) is equal to the sum of the heat entering *V* through its boundary surface and the heat generated by itself (right-hand side).

In general, steady-state temperature is of importance because, once a chip reaches that state, the temperature does not respond to an instantaneous change of power consumption. This is due to the relatively large time constant of heat conduction (a few milliseconds) compared to that of a clock cycle (some picoseconds). In a steady state, in which there is no change of temperature over time, the following equation can be solved:

$$\nabla^2 T(x, y, z) = -g(x, y, z)/\kappa, \qquad (2.3)$$

where  $\kappa$  is approximated to be constant. Note that g is typically given for each block, say A and B of Fig. 2.9(a); in other words, we approximate the power density of A to be homogeneous—this can be a source of error when the block is very big. Average power consumption (over some period of time) is used for g of (2.3), which can be another source of error, particularly when we try to obtain the maximum temperature. These limitations should be kept in mind when temperature is referred to after estimation.

There are several methods to solve (2.2) or (2.3). Numerical methods include the finite difference method (FDM) or finite element method (FEM), both of which discretize the continuous space domain into a finite number of grid points. But these methods are very slow, usually taking tens or hundreds of minutes; thus, it is not practically possible to use them in any optimization loop. Fast estimation methods do exist. A notable one is to use a *thermal RC circuit* [17]. This is a circuit built based on the analogy between heat transfer and electrical current: heat flow can be described as a current flowing through a thermal resistance, thus yielding a temperature difference analogous to voltage. Thermal resistance and capacitance are modeled on a per-block basis or, more accurately, on a per-grid basis, in which a chip is divided into a number of imaginary grids. Another fast method to solve (2.3) is to use a Green's function. It can be readily shown that (2.3) is equivalent to

$$T(\mathbf{r}) = \int_{-\infty}^{\infty} G(\mathbf{r}, \mathbf{r}_0) \left( -\frac{g(\mathbf{r}_0)}{\kappa} \right) d\mathbf{r}_0, \qquad (2.4)$$

where **r** is (x, y, z) and **r**<sub>0</sub> is a particular value of **r**. *G* satisfies  $\nabla^2 G(\mathbf{r}, \mathbf{r}_0) = \delta(\mathbf{r} - \mathbf{r}_0)$  and is called a Green's function; i.e., *G* is a Green's function if its Laplacian is a delta function. Instead of solving partial differential equation (2.3), we can use (2.4) to directly give *T* once *G* is known. The product of cosine functions [18] and the division of hyperbolic functions have been used for *G*.

# 2.4 Circuits to Reduce Dynamic Power

Many circuit techniques have been proposed to reduce dynamic power consumption. Two of them, namely clock gating and dual- $V_{dd}$ , deserve attention because of their popularity and effectiveness, and are reviewed in this section in detail. Other techniques are summarized in Sect. 2.4.3.

# 2.4.1 Clock Gating

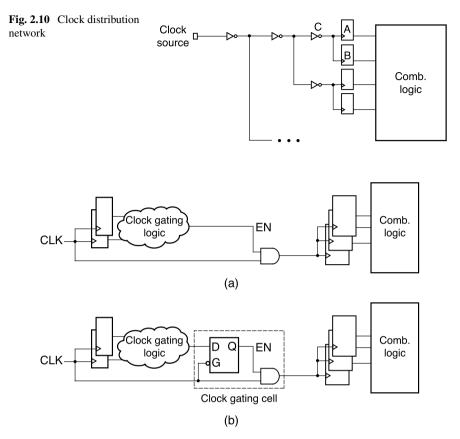

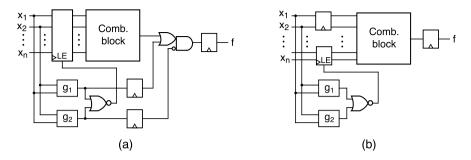

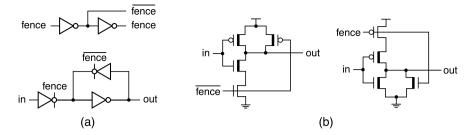

It is well known that a clock distribution network takes a large portion of total power consumption, e.g., 18% to 36% for processors and 40% for ASICs [19]. This is because the elements of the network including flip-flops (or latches) and clock buffers, as shown in Fig. 2.10, are always triggered. A simple way to reduce this consumption is to gate the clock to a flip-flop, say A, when its input and output are the same. If a clock to A and B can be gated at the same time, we may try to gate the buffer C instead, or higher stage buffers if more flip-flops can be gated together.

Conceptually, clock gating can be implemented as shown in Fig. 2.11(a). The block called clock gating logic determines when the combinational logic does not perform its computation (EN = 0) and when it does (EN = 1). Two things should be noted in regard to clock gating logic. It is an extra logic, which causes an increase of circuit area and power consumption; it therefore should be kept small as much as possible. Clock gating logic itself is a combinational logic, and it thus may generate a hazard; in particular, a static 1-hazard (a change of logic value from

Fig. 2.11 Clock gating: (a) concept and (b) implementation

1 to 0 and back to 1, for a short period of time) while CLK = 1 makes the flipflops capture their inputs when they are not supposed to. This is resolved by using a negative sensitive latch, as shown in Fig. 2.11(b). When CLK = 1, the latch is opaque and thus blocks any hazard from clock gating logic. The latch together with an AND gate are typically called a clock gating cell. Note that a positive sensitive latch and an OR gate are used if the flip-flops are falling edge triggered ones.

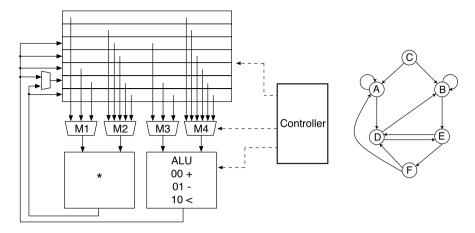

From the designer's perspective, the challenge is to design the clock gating logic such that flip-flops are gated as often as possible while the gating logic is kept small. This is done either manually by human designers or automatically by CAD tools. A generic form of digital circuit consists of a data path and controller, as illustrated in Fig. 2.12. Designers should know when each functional unit is idle from a scheduled data flow description, which could guide them to design clock gating logic. The controller is typically modeled as a finite state machine (FSM) such as the one shown in Fig. 2.12; self-loops associated with states A and B correspond to the mo-

Fig. 2.12 Digital circuit consists of data path and controller

ment when the clock can be gated; e.g., if state A is assigned binary representation 000, the register content does not change before and after the self-loop.

Automatic synthesis of clock gating logic is a bottom-up approach. Let  $\delta_i(\cdot)$  be the Boolean expression for the input of the *i*th flip-flop and let  $S_i$  be its output. The clock can be gated when these two take the same value (either 1 or 0); the clock gating logic is thus given by

$$g_i = \overline{\delta_i(\cdot) \oplus S_i}.$$

(2.5)

Implementing each  $g_i$  as a separate logic incurs too much overhead. Some  $g_i$ 's thus should be merged as much as possible. Note that if  $g_1$  and  $g_2$  are merged, flip-flops 1 and 2 are gated only when both can be gated, thereby reducing the gating probability. Therefore, merging  $g_i$ 's is a trade-off between clock gating logic and gating probability. There are other techniques to reduce the complexity of clock gating logic, e.g., using don't cares, logical approximation, and so on [20].

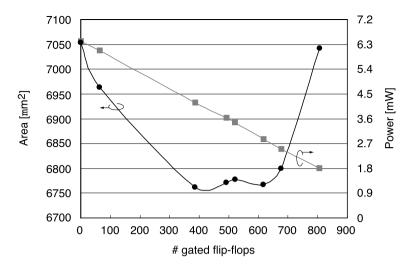

Figure 2.13 shows the result of clock gating synthesis using a commercial CAD tool [21]. Interestingly, the area starts to decrease as clock gating is applied to some flip-flops, less than 400 flip-flops in Fig. 2.13. This happens because a feedback multiplexer, which is attached to a flip-flop to retain its current value when it needs to, can be removed when clock gating is applied; i.e., if the clock is gated, the value of the flip-flop is retained anyway. This benefit is outweighed by an increasing amount of clock gating logic as more flip-flops are gated. The power consumption monotonically decreases, indicating that extra power consumption from clock gating logic is not large enough (due to the low switching activity of combinational logic) to mask the reduced power consumption of the flip-flops. Figure 2.13 suggests a trade-off between area and power consumption, which can be exploited in architectural design.

Fig. 2.13 Clock gating synthesis for wbdma [7], which contains 987 flip-flops in total

## 2.4.2 Dual-V<sub>dd</sub>

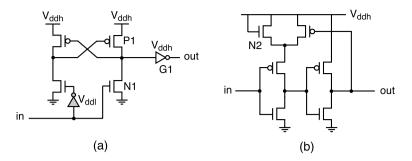

From (2.1), it is clear that the best way to reduce dynamic power is to reduce  $V_{dd}$ . However, reducing  $V_{dd}$  comes at the cost of reduced circuit speed. The alternative approach is to use two  $V_{dd}$ 's, a higher one  $V_{ddh}$  and a lower one  $V_{ddl}$ , so that  $V_{ddl}$  is used for gates that do not affect the overall circuit speed. There are several challenges in the implementation of dual- $V_{dd}$ :

- Layout architecture: gate placement is restricted in dual-V<sub>dd</sub>, which causes an increase of area and wire length.

- Level conversion: a  $V_{ddl}$  gate needs a level converter when it drives a  $V_{ddh}$  one.

- Dual- $V_{dd}$  allocation: automatic allocation of  $V_{ddh}$  and  $V_{ddl}$  must be done for the CAD tool.

- Selection of  $V_{ddl}$ :  $V_{ddh}$  is typically mandated by technology;  $V_{ddl}$  is thus a design parameter whose value should be carefully selected.

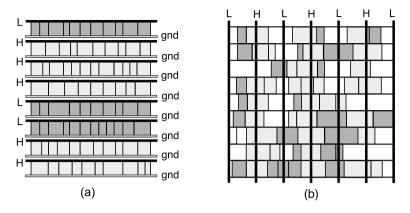

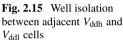

**Layout Architecture** Figure 2.14(a) shows the simplest architecture [22], where each row is dedicated to either  $V_{ddh}$  or  $V_{ddl}$  cells. Standard placement tools can be used for this architecture; once each cell is tagged for a type of row ( $V_{ddh}$  or  $V_{ddl}$ ), it can be placed. The wire length typically increases substantially [23], which makes timing closure difficult to achieve; this limits the application of this architecture. Figure 2.14(b) [24] is a layout architecture, which is less constrained as far as cell placement is concerned. However, in order to minimize well isolation (see Fig. 2.15), each of the  $V_{ddh}$  and  $V_{ddl}$  cells must be grouped as much as possible; this may be performed as a refinement step after the initial placement [24], but carefully, so that initial placement is not perturbed too much. This step must be coordinated

N-well isolation

Fig. 2.14 (a) Row-based layout architecture and (b) architecture that allows less constrained placement

with the topology of the generating power grid, so that each group can be placed directly below (or very close to) corresponding supply voltage rails.

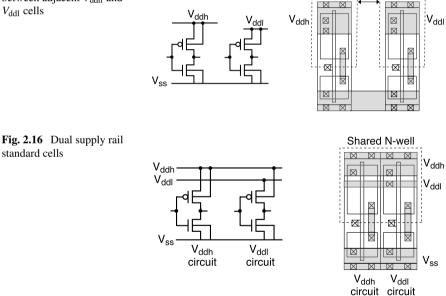

Cell placement is restricted (to a different degree) in both layout architectures of Fig. 2.14. This is unavoidable as long as standard cells developed for single  $V_{dd}$  are used for dual- $V_{dd}$  circuits. The restriction can be completely removed in the approach illustrated in Fig. 2.16 [25, 26], where each cell has dual rails for supply voltage: one for  $V_{ddh}$  and another for  $V_{ddl}$ . This of course comes at the cost of developing a custom cell library. In  $V_{ddh}$  cells, the n-well is biased to  $V_{ddh}$ , which

Fig. 2.17 Level converters: (a) pMOS cross-coupled level converter (CCLC) [22] and (b) singlesupply level converter (SSLC) [24]

is also a voltage supply. The n-well bias of  $V_{ddl}$  cells also must be made to  $V_{ddh}$ , so that adjacent  $V_{ddh}$  and  $V_{ddl}$  cells can share their n-well for area efficiency. In this setting, the pMOS transistor of  $V_{ddl}$  cells is made slower due to its negative body bias (e.g., 18% speed degradation for  $V_{ddl} = 1.2$  V with  $V_{ddh} = 1.8$  V [26]); however, its subthreshold leakage is reduced substantially. The cell height increases, as it must, but only marginally (e.g., 2.7% [25]). This is because the  $V_{ddh}$  rail can be made thinner as the amount of charge it has to deliver becomes less; the  $V_{ddl}$  rail can be made even thinner, as  $V_{ddl}$  cells are typically a small proportion of the total cells.

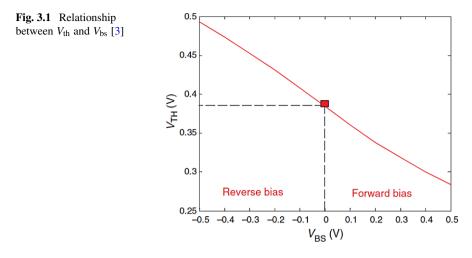

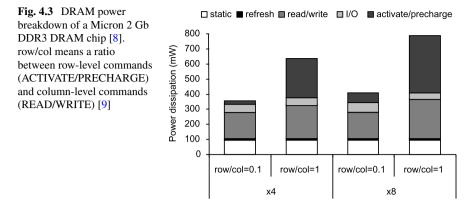

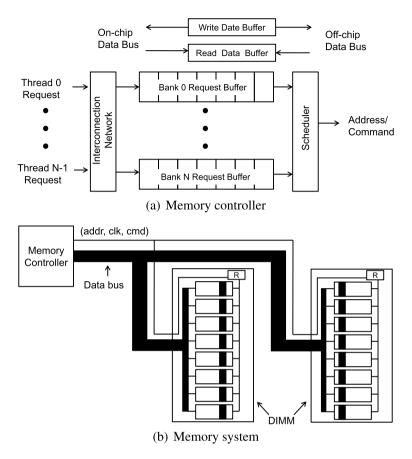

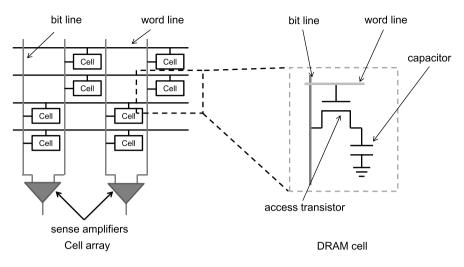

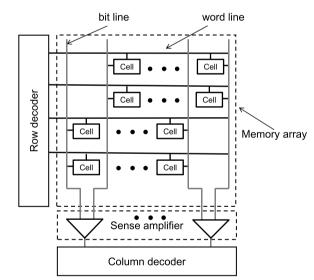

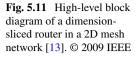

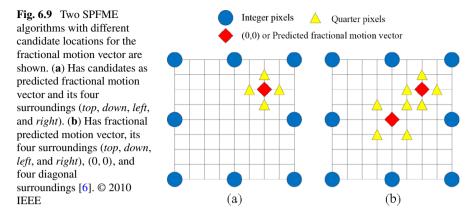

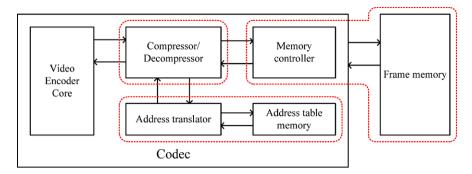

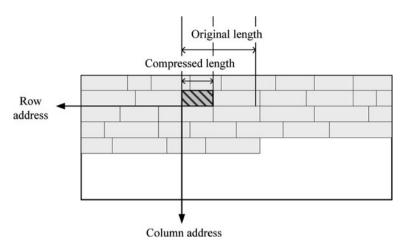

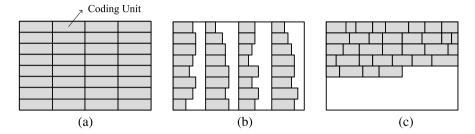

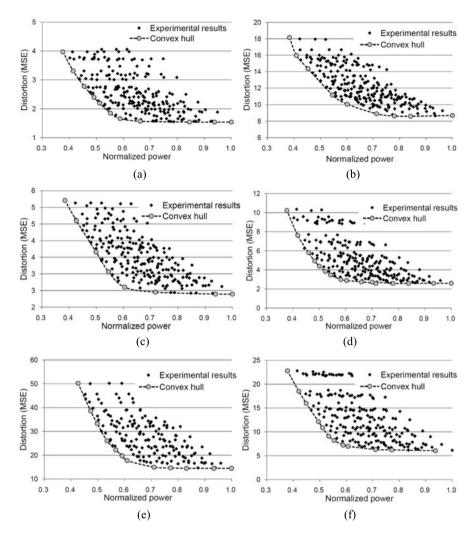

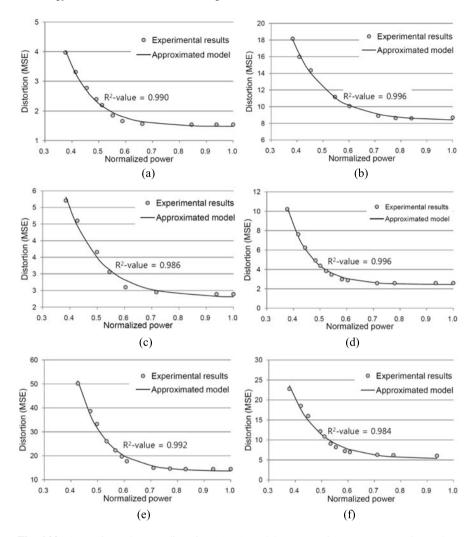

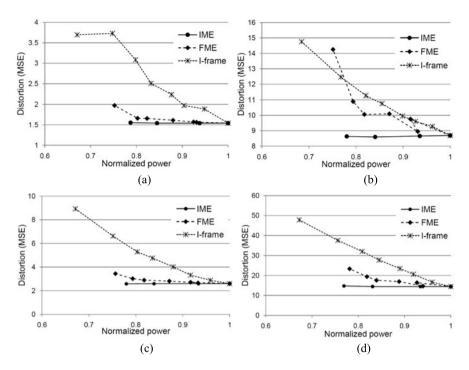

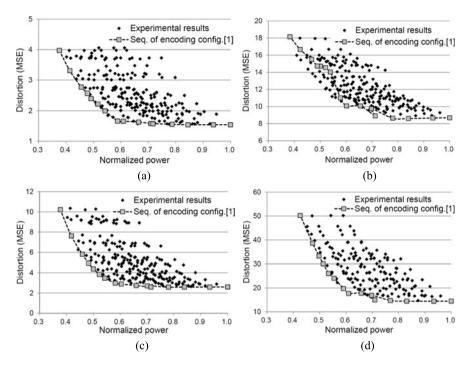

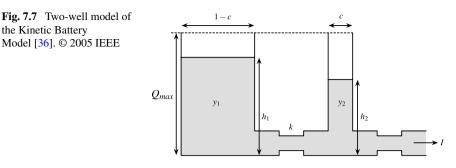

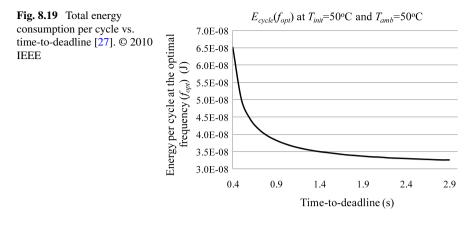

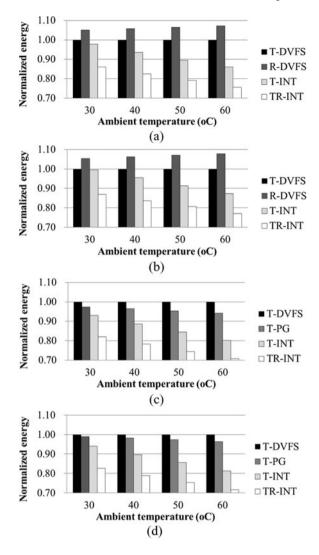

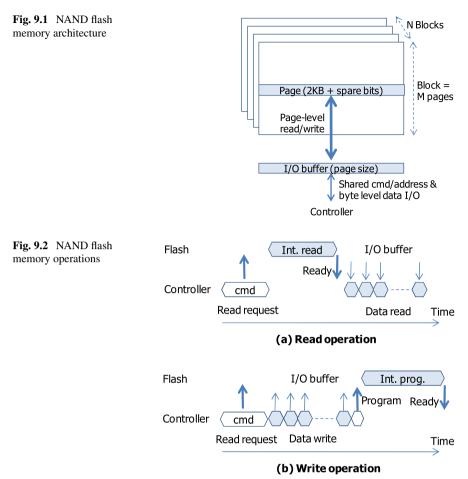

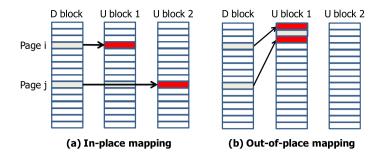

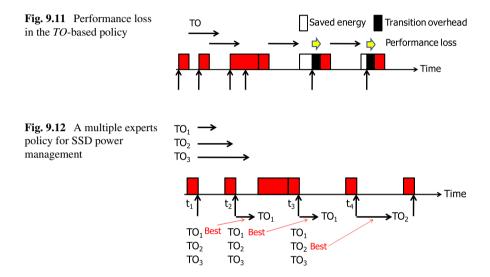

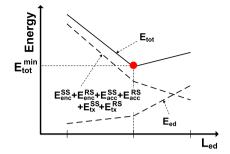

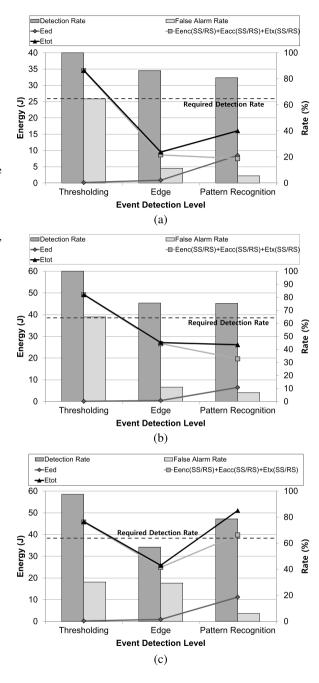

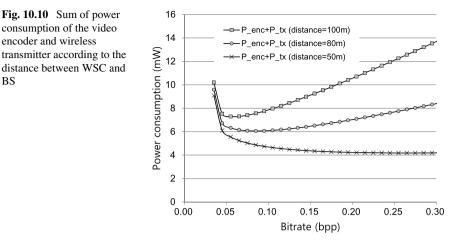

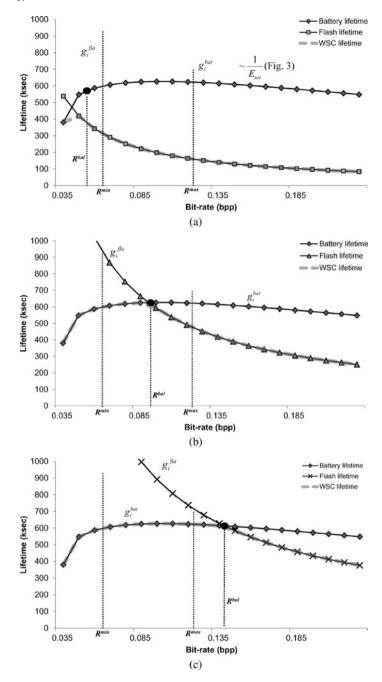

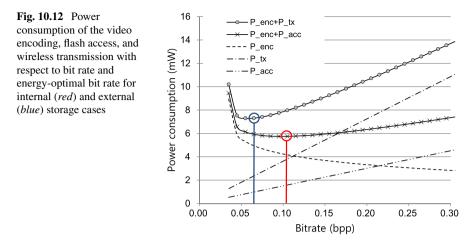

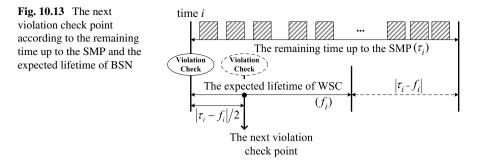

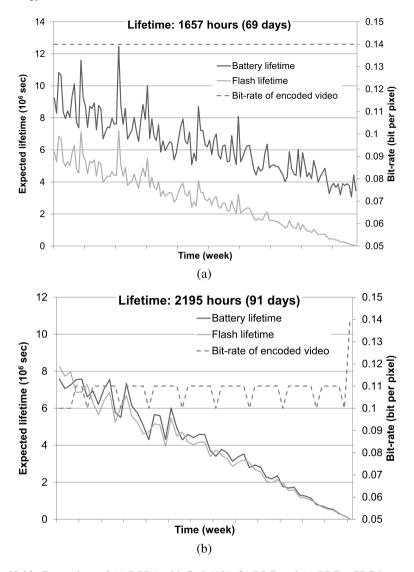

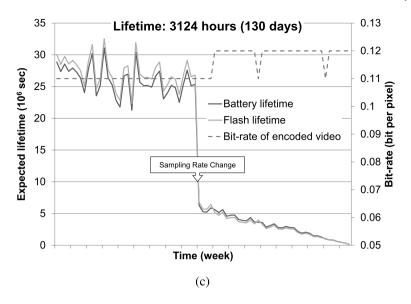

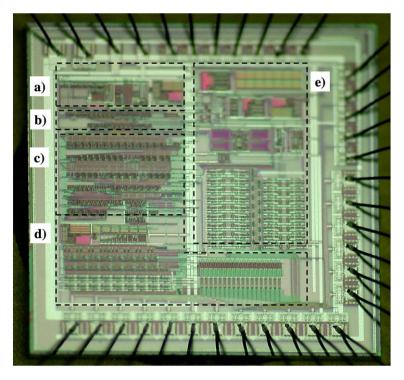

**Level Conversion** The key component of dual- $V_{dd}$  design is a level converter. If  $V_{dd1}$  is directly applied to the input of an  $V_{ddh}$  inverter, both nMOS and pMOS transistors will be turned on, if  $V_{dd1} - V_{ddh}$  is smaller than the threshold voltage of pMOS; this causes huge amount of short-circuit current. Even if pMOS is not turned on, it is only weakly turned off and incurs a large amount of subthreshold current. Therefore, a level converter must be used whenever a  $V_{dd1}$  gate drives a  $V_{ddh}$  one.